| Объявление форума |

Если пользуетесь личными сообщениями и получили по электронной почте оповещение о новом письме, не отвечайте, пожалуйста, почтой. Зайдите на форум и ответьте отправителю через ЛС. |

Полигон-2 » Технический флейм » Ищу какую-нибудь автоматизацию перевода платы в схему |

|

Ищу какую-нибудь автоматизацию перевода платы в схему

Реверс-инжиниринг старых плат

| <<Назад Вперед>> | Страницы: 1 * 2 | Печать |

| Parasite |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 13 декабря 2013 15:45 Сообщение отредактировано: 13 декабря 2013 15:46

LEON написал: Из каких соображений программа будет строить вам красивые УГО элементов и располагать их в удобоваримом для чтения варианте?Например из тех же, из каких любой вменяемый xCAD делает обратную задачу - по схеме оптимизирует расположение корпусов на плате с учетом минимализации числа переходов и длины дорожек. Опять же, deGate ж это как-то делает - но только с кристаллами..... А дорожки растяну я, так и быть - ручками (хотя, по идее - OCR и векторизацию еще никто не отменял). LEON написал: Или, что более верно как мне кажется - если знаете как работает прототип платы, то сразу в VHDL пишите.Дак вот не знаем, к сожалению. Посему - нужна схема, и желательно - безошибочная (глядишь - и до реплик дорастем).  LEON написал: А вообще интересно посмотреть на плату с парой сотен корпусов 155Да не вопрос. И там далеко не только одни 155е - там и Z80, и Ямахи, и мотороловские камни в виде "доп.процессоров".... |

| Guest |

NEW! Сообщение отправлено: 13 декабря 2013 15:58

Parasite написал: Интересует какая-нибудь автоматизация "реверс-сборки" платы (из готовой рабочей платы - в схему, и далее если повезет - в VHDL). Ручками оно всё конечно делается - но очень медленно, и схема хоть и получается, но визуально зело корявая и трудная для чтения.Интересно, как такая прога справится с многослойными платами и металлизацией via-holes? Рентген-аппарат в комплекте?!? Обычную, двустороннюю можно закинуть на сканер и обрисовать в *каде, позже добавить "прототип-чипов" и конвертнуть в схему, не так и сложно. А со многослойкой как? Топором нарубать?? |

| Сейчас на форуме |

| Parasite |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 13 декабря 2013 16:40 Сообщение отредактировано: 13 декабря 2013 16:41

Fe-Restorator написал: как такая прога справится с многослойными платами и металлизацией via-holes? Рентген-аппарат в комплекте?!?Это как раз самая простая часть - и она давно выполнена. Имеются картинки дорожек платы по всем слоям, при необходимости - могут быть векторы из них же. Проблема собственно в получении внятной схемы (разрисовке логики и прочего из всех этих мелких корпусов "на бумагу"), учитывая имеющиеся дорожки с платы. |

| LEON

Member

Откуда: Московская обл. Всего сообщений: 181 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 18 мар. 2008 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 13 декабря 2013 17:26 Сообщение отредактировано: 13 декабря 2013 17:28

Parasite написал: ...по схеме оптимизирует расположение корпусов на плате...Это разные задачи. При трассировке вы сами задаете соответствие схемного элемента и его корпуса, далее программа просто управляет правилами геометрии - оптимизирует нужные линии, расставляет кучеряво корпуса и прочее. А вам то нужно получить схему из набора связей между точками, и то, предварительно такой массив как-то нужно срисовать с платы. Как вам программа нарисует УГО резистора исходя из двух падов? А микросхему, да так, чтобы в итоге схема еще и читалась? Поэтому ручками  |

| Parasite |

LEON написал: Это разные задачи.Я понимаю. Но ведь хочется же!  LEON написал: нужно получить схему из набора связей между точками, и то, предварительно такой массив как-то нужно срисовать с платы.Я согласен его вбить в программу. Ручками. Как таблицу соединений "Отсюда>->туда" плюс расчиповку\разноговку корпусов. Я, собссно, именно этим сейчас и занимаюсь. То есть, программа таки БУДЕТ иметь схему. Просто оная будет нечитаема человеком но читаема программой (ибо ей плевать на читаемость и визуальную составляющую). Ведь даже тот же простейший Eagle уже начинает орать мне на то, что у чипа который я начал отрисовавать (выбранного из базы программы - то есть, оная знает где у него что) - еще не подключены те и вон те ноги, итд... При продолжении рисования соединений к другим ногам - вопли уменьшаются вплоть до прекращения... То есть, он прекрасно знает, как оно должно быть (при нуле варнингов). Я, наверное, не слишком точно выразился вначале: я не прошу от программы сделать вообще всё, лишь тупо показав ей плату издалека - я прошу лишь программу, которая просто отрисует (читай: сгенерирует красивую картинку) схему пред мои глазки. Красиво. А все начальные данные (чиповку, монтажку, таблицу соединений и проч) я в нее, разумеется - введу сам. Я не думаю, что задача "Взять из базы известный чип, отрисовать его на поле, и органично обрулить векторами дорожек согласно введенных юзером в таблицу". Это ведь совершенно равносильно разводке собственно платы со введенной схемы - там ведь точно то же самое: чипы (известные программе)+таблица соединений (введенная со схемы) -> генерируем печатку. Не вижу ну совершенно никакой технической проблемы в обратном процессе, так как он изначально "беспотерьный" - и никакие исходные данные не теряются, кроме камментов на исходной схеме. Те же кады автоматом полностью всю тех.документацию могут выдать...Приближаясь к программингу - это даже не дизассемблировать программу (так как компиляция таки есть процесс с безусловной "потерей исходника" - в отличие от разводки числа соединений), это как раззиповать архив обратно.  Но другой вопрос - в том, что официально такой программы быть не может: она влет нарушит целую кучу разных патентов и прочей копирастии, ибо и так понятно для чего оная может понадобиться... для невозбранного заимствования из чужих и уже рабочих и отлаженных решений.  ( ( |

| Guest |

NEW! Сообщение отправлено: 14 декабря 2013 2:41

Parasite написал: разрисовке логики и прочего из всех этих мелких корпусов "на бумагу"Т.е. ты хочешь автоматом дробить чипы на DD1.1, DD1.2, ... и т.д.? Сильно. При 150 корпусах по 4 (в среднем) элемента в каждом - думаю, ты потом замаешься определять в каком углу схемы притаился очередной кусок (.y) очередного "DDx". |

| Сейчас на форуме |

| Parasite |

Fe-Restorator написал: Т.е. ты хочешь автоматом дробить чипы на DD1.1, DD1.2, ... и т.д.? Сильно. При 150 корпусах по 4 (в среднем) элемента в каждом - думаю, ты потом замаешься определятьИменно. В том числе. А теперь представь как я замаялся делать ровно то же самое, но ручками.  Плюс, при малейшей необходимости передвинуть какой-то элемент на уже готовой схеме - за ним тянется всё больше и всё длиннее дорожек, и приходится "раздвигать" уже готовые другие части схемы....всё опять же ручками. Вот я и хочу хоть какую-то автоматизацию хотя бы этого участка работы. А то, что потом на схеме искать - так это не беда. Схема большая сама по себе, искать так и так придется. |

| alecv

Advanced Member

Откуда: Санкт-Петербург Всего сообщений: 5545 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 5 окт. 2004 |

вот тут немного http://digitalchip.ru/rabotaem...y-kartinki |

| Parasite |

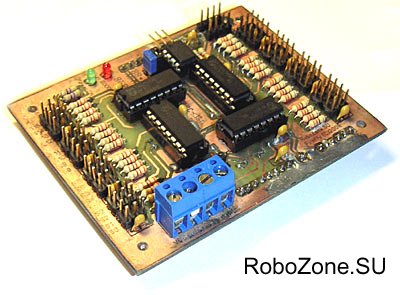

alecv написал: вот тут немногоНе. Совсем не в тему. Там просто про то, как перегнать рисунок платы с плохой бумаги в хороший редактор. Ни слова и ни намека о том, как их нее сделать схему (да и схема там изначально есть). Мне же надо из вот такого (из готового изделия, которое можно подержать в руках):  сделать вот такое (красивую, хорошую, годную схему):  То есть - ровно наоборот из того, что расписано в той статье.  PS: платы\схемы взяты просто как пример. У меня, разумеется - другие. |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

В свое время я порядочно зарисовывал двуслоек - поделюсь опытом : 1.Сначала на бумаге ( ватмане ) карандашом нарисовать УГО всех ИС исследуемой платы . 2.Собственно перенести разводку ( карандашом и, частично, ластиком ) 3.Определить ( примерно ) функционал отдельных блоков вычислительной системы. 4.Художественно отобразить все в графическом редакторе. * Т.к. прозванивать тестером с напряжением свыше 0.5 вольт недопустимо - можно в ванночке с припоем аккуратно выпаивать необходимые БИС, особенно с внутренней программой ( ПЗУ ). Если нет возможности выпаивать ИС, можно на обычный стрелочник-омметр включить германиевый диод типа Д310 в прямом направлении ( параллельно щупам ) и прозванивать в таком состоянии - вероятность выхода из строя ИС при перенапряжении менее 0.5 вольт пренебрежительно мала. * Не думаю, что программные средства для реверс-инжиниринга ПП есть хотя бы в одной фирме - т.к. возни при разработке порядочно, а плат - от силы несколько десятков - т.е. овчинка выделки не стоит. ( Ну, может, где-то в глубине континентального Китая .... ) А насчет рентгеновского аппарата - очень интересная идея. Можно, например, на кинескопе ЭЛТ монитора с разрешением 1600х1200 закрепить скотчем плату, а на плату с другой стороны - фотобумагу. Выдержку определять опытным путем. Экран ( а лучше - фотобумагу ), разумеется, заклеить черной фотобумагой для исключения фотозасветки. Начать эксперимент можно примерно с 5 минут ( ??? ). |

| <<Назад Вперед>> | Страницы: 1 * 2 | Печать |

Полигон-2 » Технический флейм » Ищу какую-нибудь автоматизацию перевода платы в схему |

|

| 1 посетитель просмотрел эту тему за последние 15 минут |

| В том числе: 1 гость, 0 скрытых пользователей |

| Последние |

|

| [Москва] LIQUID-Акция. Сливаются разъемы CF МС7004 и 7004А на AT и XT Пайка термотрубок Проммать s478 PEAK 715VL2-HT ( Full-Size SBC) Подскажите по 386 материке по джамперам. | |

| Самые активные 5 тем |

|