| Объявление форума |

Если пользуетесь личными сообщениями и получили по электронной почте оповещение о новом письме, не отвечайте, пожалуйста, почтой. Зайдите на форум и ответьте отправителю через ЛС. |

Полигон-2 » Технический флейм » Ищу какую-нибудь автоматизацию перевода платы в схему |

|

Ищу какую-нибудь автоматизацию перевода платы в схему

Реверс-инжиниринг старых плат

| <<Назад Вперед>> | Страницы: 1 * 2 | Печать |

| Parasite |

LEON написал: Это разные задачи.Я понимаю. Но ведь хочется же!  LEON написал: нужно получить схему из набора связей между точками, и то, предварительно такой массив как-то нужно срисовать с платы.Я согласен его вбить в программу. Ручками. Как таблицу соединений "Отсюда>->туда" плюс расчиповку\разноговку корпусов. Я, собссно, именно этим сейчас и занимаюсь. То есть, программа таки БУДЕТ иметь схему. Просто оная будет нечитаема человеком но читаема программой (ибо ей плевать на читаемость и визуальную составляющую). Ведь даже тот же простейший Eagle уже начинает орать мне на то, что у чипа который я начал отрисовавать (выбранного из базы программы - то есть, оная знает где у него что) - еще не подключены те и вон те ноги, итд... При продолжении рисования соединений к другим ногам - вопли уменьшаются вплоть до прекращения... То есть, он прекрасно знает, как оно должно быть (при нуле варнингов). Я, наверное, не слишком точно выразился вначале: я не прошу от программы сделать вообще всё, лишь тупо показав ей плату издалека - я прошу лишь программу, которая просто отрисует (читай: сгенерирует красивую картинку) схему пред мои глазки. Красиво. А все начальные данные (чиповку, монтажку, таблицу соединений и проч) я в нее, разумеется - введу сам. Я не думаю, что задача "Взять из базы известный чип, отрисовать его на поле, и органично обрулить векторами дорожек согласно введенных юзером в таблицу". Это ведь совершенно равносильно разводке собственно платы со введенной схемы - там ведь точно то же самое: чипы (известные программе)+таблица соединений (введенная со схемы) -> генерируем печатку. Не вижу ну совершенно никакой технической проблемы в обратном процессе, так как он изначально "беспотерьный" - и никакие исходные данные не теряются, кроме камментов на исходной схеме. Те же кады автоматом полностью всю тех.документацию могут выдать...Приближаясь к программингу - это даже не дизассемблировать программу (так как компиляция таки есть процесс с безусловной "потерей исходника" - в отличие от разводки числа соединений), это как раззиповать архив обратно.  Но другой вопрос - в том, что официально такой программы быть не может: она влет нарушит целую кучу разных патентов и прочей копирастии, ибо и так понятно для чего оная может понадобиться... для невозбранного заимствования из чужих и уже рабочих и отлаженных решений.  ( ( |

| Guest |

NEW! Сообщение отправлено: 14 декабря 2013 2:41

Parasite написал: разрисовке логики и прочего из всех этих мелких корпусов "на бумагу"Т.е. ты хочешь автоматом дробить чипы на DD1.1, DD1.2, ... и т.д.? Сильно. При 150 корпусах по 4 (в среднем) элемента в каждом - думаю, ты потом замаешься определять в каком углу схемы притаился очередной кусок (.y) очередного "DDx". |

| Сейчас на форуме |

| Parasite |

Fe-Restorator написал: Т.е. ты хочешь автоматом дробить чипы на DD1.1, DD1.2, ... и т.д.? Сильно. При 150 корпусах по 4 (в среднем) элемента в каждом - думаю, ты потом замаешься определятьИменно. В том числе. А теперь представь как я замаялся делать ровно то же самое, но ручками.  Плюс, при малейшей необходимости передвинуть какой-то элемент на уже готовой схеме - за ним тянется всё больше и всё длиннее дорожек, и приходится "раздвигать" уже готовые другие части схемы....всё опять же ручками. Вот я и хочу хоть какую-то автоматизацию хотя бы этого участка работы. А то, что потом на схеме искать - так это не беда. Схема большая сама по себе, искать так и так придется. |

| alecv

Advanced Member

Откуда: Санкт-Петербург Всего сообщений: 5545 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 5 окт. 2004 |

вот тут немного http://digitalchip.ru/rabotaem...y-kartinki |

| Parasite |

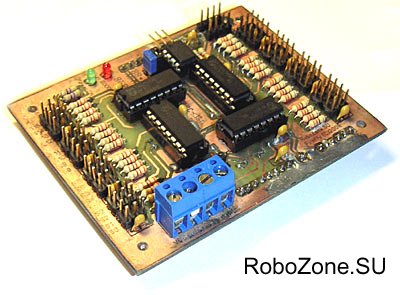

alecv написал: вот тут немногоНе. Совсем не в тему. Там просто про то, как перегнать рисунок платы с плохой бумаги в хороший редактор. Ни слова и ни намека о том, как их нее сделать схему (да и схема там изначально есть). Мне же надо из вот такого (из готового изделия, которое можно подержать в руках):  сделать вот такое (красивую, хорошую, годную схему):  То есть - ровно наоборот из того, что расписано в той статье.  PS: платы\схемы взяты просто как пример. У меня, разумеется - другие. |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

В свое время я порядочно зарисовывал двуслоек - поделюсь опытом : 1.Сначала на бумаге ( ватмане ) карандашом нарисовать УГО всех ИС исследуемой платы . 2.Собственно перенести разводку ( карандашом и, частично, ластиком ) 3.Определить ( примерно ) функционал отдельных блоков вычислительной системы. 4.Художественно отобразить все в графическом редакторе. * Т.к. прозванивать тестером с напряжением свыше 0.5 вольт недопустимо - можно в ванночке с припоем аккуратно выпаивать необходимые БИС, особенно с внутренней программой ( ПЗУ ). Если нет возможности выпаивать ИС, можно на обычный стрелочник-омметр включить германиевый диод типа Д310 в прямом направлении ( параллельно щупам ) и прозванивать в таком состоянии - вероятность выхода из строя ИС при перенапряжении менее 0.5 вольт пренебрежительно мала. * Не думаю, что программные средства для реверс-инжиниринга ПП есть хотя бы в одной фирме - т.к. возни при разработке порядочно, а плат - от силы несколько десятков - т.е. овчинка выделки не стоит. ( Ну, может, где-то в глубине континентального Китая .... ) А насчет рентгеновского аппарата - очень интересная идея. Можно, например, на кинескопе ЭЛТ монитора с разрешением 1600х1200 закрепить скотчем плату, а на плату с другой стороны - фотобумагу. Выдержку определять опытным путем. Экран ( а лучше - фотобумагу ), разумеется, заклеить черной фотобумагой для исключения фотозасветки. Начать эксперимент можно примерно с 5 минут ( ??? ). |

| Guest |

NEW! Сообщение отправлено: 14 декабря 2013 22:26

MM написал: А насчет рентгеновского аппарата - очень интересная идея. Можно, например, на кинескопе ЭЛТ монитора с разрешением 1600х1200 закрепить скотчем плату, а на плату с другой стороны - фотобумагу. Выдержку определять опытным путем.Хе. Опустим вопросы об радиоактивности, а как ты собираешься разглядеть третий из 6-ти слоёв и только его? Ежли все остальные слои непременно его экранируют собою... |

| Сейчас на форуме |

| Parasite |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 15 декабря 2013 7:42 Сообщение отредактировано: 15 декабря 2013 7:42

MM написал: 4.Художественно отобразить все в графическом редакторе.Лично меня интересует именно этот пункт. Художества пары-тройки сотен корпусов мелкой логики (по 4...6 элементов в каждом) - чем делать? Ручками? В каком конкретно графическом редакторе? В фотошопе? MM написал: Можно, например, на кинескопе ЭЛТ монитора с разрешением 1600х1200 закрепить скотчем плату, а на плату с другой стороны - фотобумагуОсспаде... Давно есть такое чудо цивизизации, как светостол и синьки. В любом конструкторском бюро - а если знать процесс, то и дома.  MM написал: насчет рентгеновского аппарата - очень интересная идея.Плохая идея. Во-первых, все предыдущие слои будут безусловно экранировать все последующие. А так как именно на поверхностных слоях как правило разведены толстые шины питания и экраны - то конец немного предсказуем. Во-вторых, Вы вряд ли сможете сфокусировать рентгеновское излучение с точностью +\-1мм (толщина между слоями в обычной, не очень современной плате). В результате вместо одного слоя на фотке получите картинку со всех них, одинаково контрастных. В-третьих, не забываем что и сами чипы тоже просветятся - и их богатое внутреннее содержимое наложится на дорожки под ними. В результате будет что-то типа такого:  Fe-Restorator написал: как ты собираешься разглядеть третий из 6-ти слоёв и только его?Только разрушающие методы. Других нет. Нагрев, верхонки, скальпель, расслоение платы. Ручками. Далее - сканы, и как обычно. Лично я именно так всегда и делаю - посему исследуемых плат всегда прошу от двух экземпляров. Больше - лучше. PS: Нашел тут вот такой софт: ----------- A Tool for Reverse Engineering With pixel images integrated into PCB data files, reverse engineering a circuit becomes as simple as placing actual parts and tracks on top of the pictures of the parts and the tracks. An assortment of pixel image processing functions are available to rotate, scale, and transform the images so they are properly grid-aligned with the real world. Once the new layout is complete, the superfluous image data can be discarded. A netlist of the actual connections can be created and a schematic data file can be produced. There is even an autorouter specifically designed for schematics. ----------- http://www.holophase.com/features.htm Ни у кого леченной версии нет? Что-то на всероссийских репозитариях не ищется... |

| xoiss |

NEW! Сообщение отправлено: 1 февраля 2019 19:26

возник подобный вопрос — поискал — нашёл эту тему... ... увы, ответа в ней на поставленный вопрос не наблюдаю "поставленный вопрос" — софт, который: 1. из платы сделает нетлист 2. по нетлисту нарисует принципиалку с первым пунктом более-менее понятно (при наличии скана можно как-то получить нетлист) а вот на второй пункт ответа не заметил по пункту 2 — суть, есть идея такого рода: - использовать для построения принципиальной схемы таки самый (почти) обычный автотрассировщик - только вместо изображений корпусов компонентов (как они выглядят на печатной плате), конечно же, использовать библиотеку УГО для принципиальных схем "нормальный" автотрассировщик позволяет задать ему некоторые ограничения, например: - как бы "плата" имеет только один слой как бы "металлизации" - и один слой как бы "джамперов" (слой джамперов для автотрассировщика, емнип — это почти как слой металлизации, только дорожки на нём трассировщик будет проводить, состоящие всего из одного прямолинейного сегмента, неразветвляющиеся, без полигонов и т.д. — то, что можно выполнить потом отрезком провода) - в описании компонента под картинкой УГО задать keep-out полигон (в таких полигонах трассировщику запрещено проводить дорожки — в реале их иногда размещают под корпусами микросхем ровно в том месте, где у микросхемы вляпан кристалл, либо если нужно сделать разделительный/электрический зазор между функциональными блоками на плате) вот... проканает или нет? и вообще, может, кто-то за прошедшие 5 лет нашёл ответ? |

| Сейчас на форуме |

| <<Назад Вперед>> | Страницы: 1 * 2 | Печать |

Полигон-2 » Технический флейм » Ищу какую-нибудь автоматизацию перевода платы в схему |

|

| 0 посетителей просмотрели эту тему за последние 15 минут |

| В том числе: 0 гостей, 0 скрытых пользователей |

| Последние |

|

| [Москва] LIQUID-Акция. Сливаются разъемы CF МС7004 и 7004А на AT и XT Пайка термотрубок Проммать s478 PEAK 715VL2-HT ( Full-Size SBC) Подскажите по 386 материке по джамперам. | |

| Самые активные 5 тем |

|