| Объявление форума |

Если пользуетесь личными сообщениями и получили по электронной почте оповещение о новом письме, не отвечайте, пожалуйста, почтой. Зайдите на форум и ответьте отправителю через ЛС. |

Полигон-2 » Другие архитектуры » DCJ11 несколько вопросов |

|

DCJ11 несколько вопросов

| <<Назад Вперед>> | Страницы: 1 2 3 4 5 6 7 8 9 | Печать |

| 1Ж24Б

Advanced Member

Откуда: Kaluga Всего сообщений: 349 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 7 нояб. 2014 |

На макетную плату запаял панельки под сборку М8К, развёл питание и кварцевый резонатор (4 МГц) с обвязкой. На шину AD15-AD0 поставил регистры ИР23. Т.е. повторил часть обвязки процессора по ссылке из первых сообщений темы. На INIT процессор реагирует. На /ALE, /SCTL, и /BUFCTL импульсы. По сигналам BS0 и BS1 получилось, что сменяются режимы обращения к УВВ и регистрами процессора/GP/статуса. После защёлкивания AD7-AD0 увидел код "002" (в восьмиричной системе). Вопрос после макетирования: как процессор обходится без подтяжки выводов AD15-AD0 ? Когда идёт чтение линий AD7-AD0 при старте, к ним подключены входа регистров (ТТЛШ) для защёлкивания, выхода приёмника 6402 в третьем состоянии и входа передатчика (КМОП). Сам процессор КМОП. Или я что-то упускаю ? |

| Guest |

NEW! Сообщение отправлено: 27 мая 2018 22:32

Регистры на AD0-AD15 ставить излишне. Вам нужно защелкнуть только BS0, BS1 AD1 и AD2. BS1 и BS2 отправляете на одну половинку дешифратора, AD1 и AD2 на вторую. Для порта вполне достаточно. Далее, шину процессора подтягивать не нужно. Там честные единица и ноль. Сам камень КМОП, но правило .8 питания у него только на тактовые пины ЕМНИП. Во всяком случае у меня он отлично работает от 3.3в CPLD. Или я не там понял вопрос? |

| Сейчас на форуме |

| 1Ж24Б

Advanced Member

Откуда: Kaluga Всего сообщений: 349 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 7 нояб. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 27 мая 2018 22:46 Сообщение отредактировано: 27 мая 2018 22:48

В даташите из AI0-AI3 и DAL7-DAL0 дешифратором формируется разрешение считать процессором конфигурацию при старте, заранее выставленную перемычками на входах буферной микросхемы LS244. На макете же она специально не задаётся. |

| Guest |

NEW! Сообщение отправлено: 27 мая 2018 22:54 Сообщение отредактировано: 27 мая 2018 22:55

Ну так я же и писал выше про наличие/отсутствие РНП. Поскольку вам сейчас достаточно просто пультовогого режима, используйте кнопку HALT. Вы в пульт попадёте принудительно. Не гарантированно по включению питания, но у вас же есть еще кнопка INIT. Так что для простого теста будет работать и так. Ну или действительно декодировать AIO, отлавливать нужный GP Read, и выставлять на шину слово начальной установки. |

| Сейчас на форуме |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 28 мая 2018 0:34 Сообщение отредактировано: 28 мая 2018 0:44

Если есть задача сделать минимальный М-ЭВМ J11 - целесообразно задать направление проектирования "переходник J11 для платы с М1801ВМ3А", или хотя бы рассмотреть такую возможность. * ИМХО - для меня J11 интересен в первую очередь как проц для графической полуплаты для ДВК, ввиду его высокого быстродействия, т.к. на упрощенной графической карте придется регулярно работать с массивом порядка 40 Кбайт ( 640х240х2 точек = ~40 Кбайт ) ( программный скролл ). Примерная конфа АП : 0-37777 - СОЗУ программ и данных, 16 Кбайт. 040000 - 157777 - экранный массив данных ( 2 страницы ), 40 Кбайт, или массив ППЗУ - при старте программа из ППЗУ переписывается в СОЗУ адреса 0-037777. Примерные ИС : ППЗУ - 1801РР1 или аналог, 2 шт. СОЗУ - 621000 - 25 нс., 2 шт. Виды разверток - ТВ или VGA. |

| 1Ж24Б

Advanced Member

Откуда: Kaluga Всего сообщений: 349 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 7 нояб. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 28 мая 2018 21:02 Сообщение отредактировано: 28 мая 2018 22:31

andyTh, для дешифрации AI0-AI3 и GP кода КР556РТ4(А) не хватит ? По сигналу /CS эти ПЗУ переключаются за 30 нс, по адресным входам за 70(45) нс. Речь о тактовой частоте процессора 4...5 МГц.  не посмотрел сразу - автор стал "гостем". не посмотрел сразу - автор стал "гостем". |

| 1Ж24Б

Advanced Member

Откуда: Kaluga Всего сообщений: 349 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 7 нояб. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 27 июня 2018 19:12 Сообщение отредактировано: 27 июня 2018 19:13

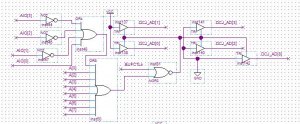

Попытка запустить советский аналог DCJ-11 частично увенчалась успехом. Что было установлено на макетную плату: - микросборка М8К ред.3, кварцевый резонатор 4 МГц - два регистра КР1533ИР23 и К555ТМ8 для защёлкивания кодов/адресов - дешифратор КР531ИД14 с КР1533ЛЕ1, К555ЛА3 и К555ЛП8 для обслуживания последовательного порта - собственно КР1002ХЛ1 и ADM202 для связи с компьютером - линии DAL0...DAL15 подтянуты к питанию резисторными сборками по 10 кОм В таком виде макет стартует после сброса INIT. После HALT на экране получаем: 177004 @ Регистры R1...R7 доступны для чтения и записи. А вот дешифратор на КР556РТ4+К555ЛЕ4, который должен при старте выдать код варианта запуска, не получился. То ли моя ошибка, то ли умерла ИС К555ТМ8, принимающая код AI0...AI3. |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

1Ж24Б написал: КР556РТ4Если можно, сделайте вариант без ППЗУ. Тогда, как более-менее получится схема, можно будет сделать переходник М8К--->М1801ВМ3А, с некотрым обвесом. Может быть даже с ~1 метром СОЗУ 0 тактов. |

| 1Ж24Б

Advanced Member

Откуда: Kaluga Всего сообщений: 349 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 7 нояб. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 27 июня 2018 20:57 Сообщение отредактировано: 27 июня 2018 22:07

ММ макет задумывался для проверки работоспособности микросборки, поскольку М8 ред. 5Б для него мертвая и не подлежит восстановлению. Места на плате хватило только для воплощения схемы от автора "хака", без ОЗУ на 16 кБ. Платы под КМ1801ВМ3 нет, после МС1201.02 и М2 решил остановиться. http://ipic.su/img/img7/fs/DSCN3816.1530121647.jpg Кварцевый генератор (К561ЛА7+кварц 153,6 кГц) для КР1002ХЛ1 не поместился. С обратной стороны примерно три слоя провода МГТФ-0,07 *точки на пластиковых микросхемах знак того, что лично проверил функционирование до пайки*. |

| <<Назад Вперед>> | Страницы: 1 2 3 4 5 6 7 8 9 | Печать |

Полигон-2 » Другие архитектуры » DCJ11 несколько вопросов |

|

| 1 посетитель просмотрел эту тему за последние 15 минут |

| В том числе: 1 гость, 0 скрытых пользователей |

| Последние |

|

| [Москва] LIQUID-Акция. Сливаются разъемы CF МС7004 и 7004А на AT и XT Пайка термотрубок Проммать s478 PEAK 715VL2-HT ( Full-Size SBC) Подскажите по 386 материке по джамперам. | |

| Самые активные 5 тем |

|

то регистр начального пуска для J11 выглядит так

то регистр начального пуска для J11 выглядит так