| Объявление форума |

Если пользуетесь личными сообщениями и получили по электронной почте оповещение о новом письме, не отвечайте, пожалуйста, почтой. Зайдите на форум и ответьте отправителю через ЛС. |

Полигон-2 » Бывший СССР » Концепт 1801ВМ1 |

|

Концепт 1801ВМ1

Неторопливая вольная фантазия в рамках приличий

| <<Назад Вперед>> | Страницы: 1 2 3 4 5 ... .. 10 11 12 13 14 15 | Печать |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

В давние времена как-то стороной прошла для меня тема Электроники-60, ДВК и прочих СМ. Не то, чтобы совсем стороной, нет, даже плату двойного размера в корзину конструировал и изготавливал, но в те времена 8-битные огрызки почему-то весь интерес переключили на себя. Похоже, что там просто потенциальный барьер вхождения банально ниже. Время прошло, а пробел остался. Поэтому долго вынашивал идею сконструировать что-нибудь на чем-нибудь из ряда 1801ВМ1/2/3. Гонял их всех на стенде, смотрел временные диаграммы, примеривал разную периферию, контроллеры памяти типа 1810ВТ3, 588ВГ2, разное из серии 1801ВП1. Выжать максимум быстродействия и максимум размера памяти - такой задачи не стояло, цель была сделать что-то более-менее сбалансированное, гармоничное, показательное и не потерявшее духа архитектуры PDP-11. В конце концов выбор остановился на 1801ВМ1. Он не провоцирует на извращения, и если не мудрить и согласиться с предлагаемой им концепцией, то, как мне показалось, он вполне сможет за это отблагодарить. У ВМ1 существует не так явно выраженная привязка к внешним средствам обеспечения его полноценного функционирования. Причем привязка плотная. В простом изделии эту привязку можно было бы игнорировать, но это вызвало бы ограничения и условности при программировании, а мне подобные ограничения не нравятся: команда у процессора есть, а в программе ее применять нельзя. После размышлений, экспериментов и прикидок того, как оно в результате будет выглядеть целиком, принял решение использовать контроллер ОЗУ 1801ВП1-030 с совмещенными функциями системного контроллера: он как раз предоставляет те самые внешние средства и обладает приемлемым для 1801ВМ1 временем отклика на обращение к ОЗУ. К тому же было желание сделать накопитель ОЗУ на 565РУ3. Таким образом, обозначилось ядро процессора, состоящее из 1801ВМ1, 1801ВП1-030 и ПЗУ 573РФ3 или 1801РР1. Для завершения картины к этому набору нужно добавить ОЗУ с ее буферными регистрами, в результате получается модуль, имеющий интерфейсом только шину МПИ. У такого модуля достаточно плотная топология электрических соединений, в одну шину не вытягивается из-за универсальности ВП1-030 и клубка вокруг ОЗУ. В одноплатной реализации трудно обеспечить компактность модуля, небольшие емкости шин и длины трассировки. Поэтому я сделал этажерку из 4 плат 100x80. Одна плата это процессорное ядро из 3-х БИС с мелкой логикой. На ней расположен наружний разъем МПИ и разъемы присоединения накопителя ОЗУ: AD0-AD15, мультиплексная адресная шина, управление, питание. Вторая плата это буферы данных-адреса-управление ОЗУ, две остальных - половинки накопителя по 16 к слов каждая. Никаких усилителей внешней шины не применяется, выходы МОПовских микросхем присоединяются к ней непосредственно, это очень нехорошо, но для разового проекта индивидуального пользования пойдет, если никому не позволять хватать руками. Карта памяти следующая, вопреки обычаям, ОЗУ в режиме USER сделано большего размера: USER 000000 .. 172776 ОЗУ (30.75 к слов) HALT 000000 .. 157776 ОЗУ (28 к слов) 160000 .. 163776 ПЗУ ODT (1 к слов) 164000 .. 172776 ПЗУ с утилитами/тестами или ОЗУ (1.75 к слов) Верхняя область, одинаковая для обоих режимов 173000 .. 173776 ПЗУ загрузчика (256 слов) 174000 .. 177576 Регистры ВУ (960 слов) 177600 .. 177676 Служебное ОЗУ (32 слова) 177700 .. 177776 Регистры для нужд процессора (32 слова) Сейчас изготовлено 4 платы, спаял две, ядро процессора и буферы ОЗУ. На время отладки хочу вместо РУ3 поставить РУ6, давным-давно был печальный опыт с выгоранием множества РУ3, когда пропало напряжение питания подложки. ODT aka Пульт при запуске у меня ОЗУ вначале не использует, сперва проверяет наличие регистра терминала, потом вычисляет контрольную сумму области ПЗУ ODT, сравнивает ее с эталоном, выдает на терминал результат проверки, потом проверяет наличие работающего ОЗУ в служебной области, выдает на терминал результат проверки и только после этого запускается пульт. Если что-то из этого не проходит, то программа сваливается в бесконечное чтение SEL2 в цикле. Это чтобы можно было осциллографом смотреть импульсы на SEL2. Вчера на макетную плату поставил 1801ВП1-065, вывел ее шиной на разъем МПИ процессорного модуля, подсоединил щуп осциллографа к ноге TF -065, включил и увидел на экране телеграфную посылку. Порасшифровывал, первые два символа CR LF, все так и должно быть. Хм, с первого раза увидеть телеграфную посылку, нечасто случается. То есть, регистры откликаются, содержимое читается, нужные данные пишутся и отсылаются. Или это знак?  Теперь надо на макетку поставить преобразователь в уровни RS232, на плату напаять хотя бы старшую половину накопителя ОЗУ и включить еще раз, уже с присоединенным настоящим терминалом. Оказывается, 1801ВП1-065 шлет символ с двумя стоповыми битами. Значит, у терминала тоже нужно будет сделать формат посылки с двумя стопами. На 10% хуже, чем с одним стопом, но тут ничего не поделаешь. Продолжение следует ... По мере продвижения ... |

| MC68k |

Mixa написал: 8-битные огрызки почему-то весь интерес переключили на себя. Похоже, что там просто потенциальный барьер вхождения банально ниже.Там была публика попроще, без моноклей. И информации было гораздо больше. Это если мы говорим про вторую половину 80х и начало 90х. Mixa написал: В конце концов выбор остановился на 1801ВМ1. Он не провоцирует на извращения, и если не мудрить и согласиться с предлагаемой им концепцией, то, как мне показалось, он вполне сможет за это отблагодаритьА еще он самый дешевый. Mixa написал: Поэтому я сделал этажерку из 4 плат 100x80.это тяжелое наследие концепта ардуино, а размер связан с ценой изготовления плат, верно? Mixa написал: Сейчас изготовлено 4 платы, спаял две, ядро процессора и буферы ОЗУ.А где СЛАЙДЫ?! Продолжайтесь. Сырки будут, или проект закрытый, для личного пользования? |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Mixa написал: Оказывается, 1801ВП1-065 шлет символ с двумя стоповыми битами.Это задаётся коммутацией её 7й ножки. |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

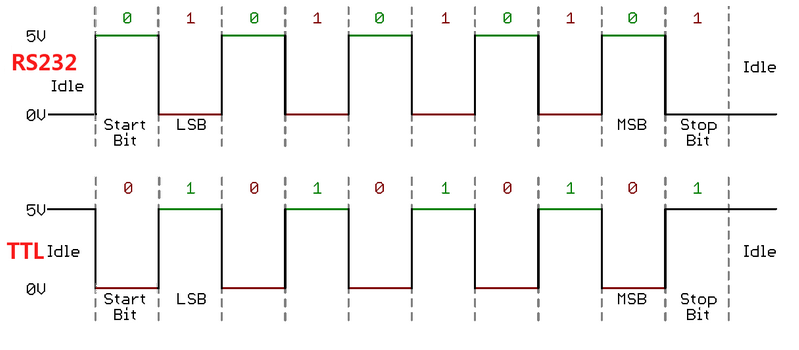

Mixa написал: Теперь надо на макетку поставить преобразователь в уровни RS232Если оставаться в стиле минимализма - на роль согласователя с RS-232 вполне годится обычный инвертор. Подробнее ЗДЕСЬ  |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

_Patron_, вот у меня на работе отечественные гибридки-драйверы rs232 при одностороннем сигнале, укладывающемся по максимуму в 3..15в, в break встают до резета, после первого же возврата с +15..3 к нулю и обратно к +3..15, без перехода к отрицательному напряжению в линии... Не надо так народ развращать... |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 2 октября 2017 20:39 Сообщение отредактировано: 2 октября 2017 21:27

Anonymous написал: _Patron_, вот у меня на работе отечественные гибридки-драйверы rs232 при одностороннем сигнале, укладывающемся по максимуму в 3..15в, в break встают до резета, после первого же возврата с +15..3 к нулю и обратно к +3..15, без перехода к отрицательному напряжению в линии... Не надо так народ развращать...А у той PC, которую мы на днях подключали - порт работает как у большинства PC и инвертора оказалось вполне достаточно. Я по наивности тоже сначала агитировал народ на что-нибудь монстровое, но меня все дружно пристыдили тем, что якобы уже давно все производимые микросхемы COM-портов для PC не различают 0в и -12в. |

| Andrei88

Advanced Member

Откуда: Пермская обл. г.Пермь Всего сообщений: 419 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 12 апр. 2008 |

Прошу прощения за оффтоп, но 2Anonymos - можно обнародовать название гибридок? |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 2 октября 2017 22:12 Сообщение отредактировано: 2 октября 2017 22:25

Они свежей разработки и с ВП, потому, наверное, нельзя. p.s. гибридка rs232>-->rs485 с высоковольтовой изоляцией. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 3 октября 2017 1:27 Сообщение отредактировано: 3 октября 2017 13:22

Присоединил DB-9. _Patron_, спасибо за подсказку, так и решил пока на макетке ТТЛ-овскими уровнями обойтись. (Но я так никогда не делаю, ни-ни, вы не подумайте!!). Это же не навсегда, только для макетки и отладки, цифровые боги, наверное, не возмутятся, в конечном варианте все будет с нормальными уровнями. Тем более диодики из 60-х, спаянные с ТЭЗов какой-то ЭВМ. Даже инверторы не потребовались, полярность сигналов у ВП1-065 уже в нужной ориентации. Макетку использовал ту, про которую давным-давно упоминал тут на форуме (почти 3 с половиной года назад это было, но нам же не к спеху, правда?  ) )На передачу поставил резистор 1 кОм, на прием тоже 1 кОм, но с ограничением диодами в пределах от 0 до питания. Вполне себе и конвертером распознается, и 065-ой принимается. (по крайней мере RR нога 31 взводится при нажатии клавиши терминала). Наблюдал сегодня живые сообщения от программы начального пуска  Пока что это выглядит неказисто, извините за отсутствие художественности. Но оно реально шевелится! Дальше - напаивать РУшки и собирать этажерку.  Anonymous, 7-я нога у меня к +5 подтянута, но говорят, она заведует форматом 7 или 8 бит. Я попробую его переключить на землю, расскажу, что получится. Vslav здесь утверждает, что стопов всегда два. MC68k, да, речь как раз про границу 80-х и 90-х, было иное мировосприятие. Размер плат из Eagle перешел. Схему рисовал там, начал предварительно размещать - а размерчик что надо, ну и оставил. С этажеркой покруче будет, это тяжелое наследие прошлого тяжелого наследия. Вторая самоделка была по мотивам Микро-80, в ней тоже разнес управление накопителем и накопитель по разным платам (кстати, именно там РУ3 массово пожег). Но там не этажерка была, а лишние сигналы на общем разъеме. Сейчас КМК симпатичнее вышло. Но - рановато об этом, надо, чтоб оно зашевелилось дальше. Выложился с неоконченным изделием, в том числе, чтобы и подстегнуть себя чуть-чуть. Полностью выкладывать проект - ну кому нужен сплошной нестандарт, у меня, вон, шина на МРН-44 разведена. А так, секретов нет. |

| MC68k |

Mixa написал: Пока что это выглядит неказисто, извините за отсутствие художественности.ПЗУшка одна  Mixa написал: MC68k, да, речь как раз про границу 80-х и 90-х, было иное мировосприятие.Бытие определяет сознание? Или наоборот?  Mixa написал: Полностью выкладывать проект - ну кому нужен сплошной нестандарт, у меня, вон, шина на МРН-44 разведена. А так, секретов нет.Было бы интересно посмотреть на обильно откомментированные куски кода. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Да, я уже позабывал все эти ВП1, у 35 5/7/8 бит 7 и 8 ноги делали, у 65 только 7 ногу оставили. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

MC68k написал: ПЗУшка однаЗато какая. В свое время штук 5 или 6 раздобыл, но они преподнесли неприятный сюрприз, такой, что и питания 5В не хватает для уверенного считывания, и куча нерабочих областей. Эта единственная из всего набора, которая в стёртом состоянии показывает 0FFFFh по всему полю, за исключением некоторых битов. Пришлось в исходнике перемещать туда-сюда фрагменты, чтобы в объектнике нолики совпали с готовыми ноликами ПЗУшки. (они там логические 1 из-за инверсии, но не суть). Короче, ужас меня охватил, что у меня эта ПЗУшка по сути единственная, и если что, то с конструктивом пролетаю. К счастью, недавно разжился небольшим запасом 1801РР1, говорят, они в целом получше себя ведут по сравнению с РФ3. MC68k написал: Было бы интересно посмотреть на обильно откомментированные куски кода.Потом, не настал еще момент "и увидел он, что это хорошо", ну, не я и не он, конечно, просто бывает такой момент, после которого это уже не выглядит как необработанная заготовка. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 3 октября 2017 20:46 Сообщение отредактировано: 3 октября 2017 20:47

Mixa написал: В свое время штук 5 или 6 раздобыл, но они преподнесли неприятный сюрпризТак у вас не РФ3, а РФ32, судя по фото, а они заведомо битые, для того и такая маркировка. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Anonymous написал: Так у вас не РФ3, а РФ32, судя по фото, а они заведомо битые, для того и такая маркировка.Это да, есть такое. Но по факту не ужас, а ужас-ужас, в остальных в основном не юзабельны обе половинки. И по характеру неюзабельности даже нельзя сказать, РФ31 она или РФ32. Вчера посмотрел, маркировки и 32 есть, и 31. Но именно этот экземпляр вроде неплохо себя показывает. Стирается, правда, жуть как неохотно. (Наверное, это она демонстрирует, что заряд на плавающих затворах хорошо держится). Программировал пол-года назад, информацию держит. Запаял половину накопителя, 16 штук РУ3. И еще одно чудо случилось, ODT заработал! (наверное, это еще один знак. Пытаюсь сообразить, к чему он. Скорее всего, к тому, что придется так и оставить там РУ6. Ну да ладно, концепция только чуть поменяется. Главное, что она не исчезнет и не размажется, этот проект же как концепт позиционирован). Пока это рабочая примерка, даже без блокировочных конденсаторов по питанию у РУ6. Дальше доустанавливаю эти кондеры и запаиваю вторую половину. Вообще, РУ6 мне в свое время понравились, эдакие простые безглючные рабочие лошадки, такое от них впечатление было. А у этих еще и знак качества на упаковке. Промежуточный итог: 1801ВМ1 рабочий, умеет исполнять команды, в том числе системные, которые используют ячейки по специальным адресам. 1801ВП1-030 рабочая, умеет управлять динамической памятью и картой адресного пространства. 1801ВП1-065 тоже рабочая, через нее происходил диалог с ODT. Из серии 1801 еще есть ВП1-034 в режиме 16-разрядного буфера-защелки для данных из памяти, она по факту тоже исправна и функционирует без замечаний. И программа ODT тоже рабочая оказалась, хотя отлаживалась на модели ДВК с процессором ВМ1 в эмуляторе от _Patron_. Уважаемый _Patron_, вам огромное спасибо за такую полезную программу! |

| Korchagin

Advanced Member

Вырыватель байтов с мясом Откуда: Понемногу отовсюду Всего сообщений: 554 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 4 апр. 2015 |

Интересно, базовый адрес микросхем РФ3 после программирования можно стереть ультрафиолетом и запрограммировать на другой? |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Ну вот, запаял вторую половину ОЗУ, все блокировочные конденсаторы, отмыл от флюса, соединил все платы - и всё, работает! ODT немного расширенный у меня: Q если без числа впереди, то дамп регистров, если с числом, то дамп области памяти M показать причину, почему оказались в ODT Че дальше-то делать?  Наверное, тест памяти нужно какой-нибудь загрузить и оставить проверяться. Наверное, тест памяти нужно какой-нибудь загрузить и оставить проверяться.И вот что ещё, форму сигнальчиков в разных местах посмотреть ещё надо, у меня ж концепт, один из пунктов которого - форма сигналов должна быть хорошая. Поэтому 4-слойка, земля сплошным слоем, питание +5 сплошным слоем, сигнальные проводники на наружных слоях. И без переходов, переходы только на ногах деталей. Промежуточный итог: Работающий процессорный модуль в габаритах 10х8х5 см, с функциональностью примерно как М2, только ОЗУ около 31 кило слова. ODT ROM OK ODT RAM OK *** 1801BM1 Macro ODT V1.0 *** @Q R0=000000 R1=000000 R2=000000 R3=000000 R4=000000 R5=000000 R6=000000 R7=000000 RS=000340 P7 .... @M000000 Power On @0Q 000000: 000000 000000 000000 000000 000000 000000 000000 000002 000020: 000000 000000 000002 000002 000000 000000 000002 000000 000040: 000000 000000 000002 000000 000000 000000 000000 000000 000060: 000000 000000 000000 000000 000000 000000 000000 000000 @100000Q 100000: 000002 000002 177777 000002 000002 000002 000002 000002 100020: 000002 000002 000002 000002 002002 002002 002002 000002 100040: 000002 000002 000002 000002 000002 002002 000002 000002 100060: 000002 000002 000002 000002 000002 000002 000002 000002 @177560Q 177560: 000000 000161 000000 000060 ? @M000200 Bus error @1000/177777 12701 001002/177777 111111 001004/177777 12702 001006/177777 22222 001010/177777 12703 001012/177777 030303 001014/177777 12704 001016/177777 040404 001020/177777 12705 001022/177777 050505 001024/177777 12706 001026/177777 060606 001030/177777 0 @1000Q 001000: 012701 111111 012702 022222 012703 030303 012704 040404 001020: 012705 050505 012706 060606 000000 177777 177777 177777 001040: 177777 177777 177777 177777 177777 177777 177777 177777 001060: 177777 177777 177777 177777 177777 177777 177777 177777 @1000G 001032 @M100000 Halt @Q R0=000000 R1=111111 R2=022222 R3=030303 R4=040404 R5=050505 R6=060606 R7=001032 RS=000340 P7 .... @RS/000340 347 @Q R0=000000 R1=111111 R2=022222 R3=030303 R4=040404 R5=050505 R6=060606 R7=001032 RS=000347 P7 .ZVC @ |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Mixa написал: Че дальше-то делать?Можно загрузить RT-11 через терминальный порт и позапускать всякие программы. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

_Patron_ написал: Можно загрузить RT-11 через терминальный порт и позапускать всякие программы.Пока не буду соблазняться. В планах, реализация которых все ближе, подключить IDE хард, причем с DMA, и DMA будет 588ВТ2. А вот линия RPLY с ее проводным ИЛИ и двунаправленностью, реальная проблема для слабеньких открытых стоков.. У меня два активных на шине будет, не только процессор. Концепция под угрозой, точнее ее пункт "без нецелесообразных задержек на шине". Но есть еще пространство для маневра, сейчас RPLY к питанию притянуто 4,7 кОм. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Был один пунктик концепции - схема без косяков и как следствие, плата без исправлений. Не срослось. Поменялось на: исправления - минимальные, малозаметные и красивые схемотехнически и логически. Исправлял привязку RPLY к фазам тактирования. Был косяк непростительный. Решил, что оптимальным вариантом будет привязка в середине каждого полутакта CLK. Распространение получила привязка активации RPLY к спаду CLK, чтобы быть зафиксированной по фронту CLK. Привязка в середине каждого полутакта обеспечивает положение фазированного RPLY к тому же фронту CLK, при этом исходное RPLY может даже на четверть такта запоздать. Это определенно положительный момент. Фазировка деактивации RPLY приводит к задержке RPLY процессору, что может привести к задержке снятия SYNC, но не более, чем на 1 такт. Практика показала, что такая вариация снятия SYNC в целом не влияет на длительность цикла шины. (И чего я к этим тактам привязываюсь? Тяжелое наследие простейших синхронных шин и идиосинкразия к сигналу типа READY, в стиле READY - для слабаков! Не, надо быть выше этого) Да, все-таки проводное ИЛИ RPLY красиво логически, красиво схемотехнически, но тяжеловесно физически. Но, что поделаешь, придется принять как есть. Размазанную было концепцию фиксируем как: шина МПИ, слаботочная, асинхронная. И на этом расслабляемся. Недостатки получаем в довесок, но не ропщем, не жалуемся, принимаем стоически ради логической и схемотехнической лаконичности. |

| Venya_Fox

Advanced Member

Откуда: Москва, Зеленоград Всего сообщений: 1055 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 11 апр. 2013 |

Они свежей разработки и с ВП5559ИН** какая нибудь? На них инфа открыта же |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Venya_Fox написал: 5559ИН** какая нибудь? На них инфа открыта жеНет, со штатными горя нахлебались, на упомянутые выше - серии нет, только шифр КБ, заказ мелкосерийный. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Пытаюсь встроить в концепцию 588-ю серию, в частности, КПДП 588ВТ2. Несколько озадачен логикой его работы. Сеанс ПДП запрашивается извне, сигналом /RQ. В ответ на шину устанавливается /DMR, ожидается /DMGO, потом /SACK, происходит цикл обмена, /SACK снимается. Вроде все последовательно и логично. Сигнал /RQ может быть снят, как только появился /DMR, этот запрос запоминается. Но может быть снят и по приходу /DMGO или /SACK. Все бы хорошо, если бы не одно но. Цепочка этих событий рушится пролетающими по шине /RPLY. Они на шине есть, они не могут не пролетать. Сценарий 1. Пришел /RQ, выставился /DMR, /RQ за ненадобностью снят, ждем /DMGO. До прихода /DMGO пролетает какой-то /RPLY. Этот /RPLY сбрасывает /DMR и запрос ПДП отменяется. На этом все заканчивается, запрос нужно выставлять заново. Какой-то осмысленности в таком поведении нет. Дальше даже и думать не хочется.  Сценарий 2. Пришел /RQ, выставился /DMR, /RQ не снимаем до прихода /DMGO или /SACK. Ждем /DMGO. До прихода /DMGO появляется /RPLY. Этот /RPLY сбрасывает /DMR, но по снятии /RPLY /DMR появляется снова (потому что /RQ все еще активен). Такие снятие-активизации /DMR по пролетающим /RPLY продолжаются до тех пор, пока не придет /DMGO. В целом в этом случае сеанс ПДП происходит как нужно, все циклы ПДП получаются в необходимом количестве, сбоев и записи мусора не замечено, но также непонятна логика за этим поведением. Человеческими словами это описывается так: -> Есть запрос (выставим DMR) (Так, у меня RPLY, DMR снимаю, все равно во время RPLY ты ничего не сделать не сможешь) (RPLY кончился, ты еще запрос не снял, что ж, выставим DMR снова) (А, не, еще один RPLY, запрос снимаю, потерпи) (Все, кончился, снова выставляю) ... >- Во, пришел ответ, шину занял, снимай запрос (а что DMR дергался, ты и не заметил, гы) -> Запрос снял Ну бред какой-то и скрытое издевательство. Не вяжутся эти все метания с концепцией мы медленно, медленно спустимся. Выходит, ВТ2 нужно будет изолировать от чужих RPLY. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Вообще-то ориентация буфера управляющих сигналов меняется по SACK и ВТ2 в любом случае изолирован от внешних RPLY, пока не захватит шину. T.к. до тех пор, пока не появится SACK, как реакция на DMGO, SYNC/DIN/DOUT/WTBT являются входными сигналами для платы, а RPLY - выходным. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Электрически RPLY у меня сейчас одна общая цепь, и двунаправленных буферов нет. МПИ между микросхемами напрямую, без развязок. В концепции поначалу и межплатных буферов не было, потому что все компактное и не развесистое. Но интеграловцы побуждают всю их 588-ю увести за буфера. Хотя бы из-за того, что у них шина АД не инверсная. |

| andyTh |

NEW! Сообщение отправлено: 18 октября 2017 18:35 Сообщение отредактировано: 18 октября 2017 18:36

Так оно ж идеологически так должно быть. Пассивное устройство от принимает сигналы от активного. Как вы планировали рулить направлением SYNC, DIN, DOUT? Вот так же надо завязать и RPLY. |

| Сейчас на форуме |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

andyTh написал: Как вы планировали рулить направлением SYNC, DIN, DOUT?Пока никак не планировал, не было нужды. И если идеологически так, то и замечательно, у меня концепт как раз идеологический. Правда, не всякая идеология вписывается, но эта - то, что надо. andyTh написал: Вот так же надо завязать и RPLY.Угу. А кстати, как "взрослые" КПДП реагируют на неприход RPLY? И на попытку обратиться к области, которая выбирается по BS? |

| andyTh |

NEW! Сообщение отправлено: 18 октября 2017 19:02

Mixa написал: Пока никак не планировал, не было нужды.Во все моменты времени, пока некая плата не хочет ПДП, сигналы SYNC, DIN, DOUT являются для неё входными, а RPLY выходным. Таким образом плата не видит чужих RPLY. А во время захвата шины направление сигналов меняется на противополоное. Т.е. какое то разделение должно быть. Не может вход микросхемы резко стать выходом  |

| Сейчас на форуме |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Mixa написал: А кстати, как "взрослые" КПДП реагируют на неприход RPLY? И на попытку обратиться к области, которая выбирается по BS?Точно так, как и процессор - ждут какое-то время ответа, затем выставляют флаг ошибки шины в регистре состояния, при этом замораживается счётчик адреса и переданных слов, чтоб можно было понять, на чём мы остановились, шина возвращается процессору и дёргается прерывание от устройства. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 18 октября 2017 20:54 Сообщение отредактировано: 18 октября 2017 23:23

andyTh написал: Во все моменты времени, пока некая плата не хочет ПДП, сигналы SYNC, DIN, DOUT являются для неё входными, а RPLY выходным.Здесь ключевое слово "плата"  Поначалу концепция представлялась как набор маленьких-маленьких плат, которые вставляются в маленькую-маленькую корзину, на разъемах разведена МПИ, платы функционально разделены, а специального умощнения не делается, потому что все маленькое и несерьезное. Заложился на нагрузочную способность самих микросхем. То есть, плата процессора, плата памяти, плата ИРПС, плата с КПДП и IDE, плата еще чего-нибудь. ИРПС в такой концепции это ВП1-035/065, с незначительной обвязкой. 588ВТ2 тоже более-менее в концепцию ложился (только АД нужно инвертировать), и направлением своих сигналов сам управляет. По мере реализации оказалось, что процессор, контроллер ПЗУ и ОЗУ неразделимы, в связке, кроме МПИ, много других сигналов, которые на разъеме не нужны. Поэтому возникла этажерка. Сейчас вот вырисовывается, что ВТ2 и всю 588-ю компанию нужно за забор поместить. И это даже хорошо, потому что глядя на пологость некоторых фронтов (которые ОК или ОС), хочется сказать стоп, шина почти на пределе. Anonymous написал: Точно так, как и процессор - ждут какое-то время ответа, затем выставляют флаг ошибки шины в регистре состояния, при этом замораживается счётчик адреса и переданных слов, чтоб можно было понять, на чём мы остановились, шина возвращается процессору и дёргается прерывание от устройства.Я вот еще хочу запретить КПДП обращаться по шине к пространству УВВ. То есть всякий select УВВ разрешить, если активен BSY процессора (или неактивен SACK). У 588ВТ2 есть вход ошибки. Импульс на нем завершает текущую пересылку, вырабатывается аппаратное прерывание и взводится триггер ошибки, его значение читается битом 14 в регистре состояния. Вот туда можно завести ошибку таймаута на шине. Еще один вход есть, RQINT называется, "Запрос прерывания". Низкий активный уровень на нем завершает текущую пересылку, вырабатывается аппаратное прерывание. Пока уровень низкий, он читается единицей в бите 13 регистра состояния. Причем еще есть бит 15, который читается как ИЛИ битов 13 и 14. Интересно, какое прерывание имели в виду разработчики этой микросхемы? P.S. ВТ2 вырабатывает аппаратное прерывание по окончании пересылки блока, но между этим настоящим прерыванием и тем RQINT никакой связи не обнаружилось. P.P.S. Постскриптум не читать, это была старая, древняя инфа, сейчас провел эксперимент и был приятно удивлен тем, что на ER и на RQINT есть вполне симпатичная и полезная реакция. Текст выше — исправил. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 18 октября 2017 22:51 Сообщение отредактировано: 18 октября 2017 23:03

Бит 15 служит для облегчения проверки в драйвере, была ли ошибка или успешно завершённая операция вызвала прерывание, делается TST @#CSR и затем BMI на обработку ошибки. А вот биты 13 и 14 показывают тип ошибки, один показывает, что ошибка случилась в контроллере ПДП - т.е. ошибка шины, а другой бит - что ошибка возникла в устройстве, которое использовало ПДП. Как вариант, ошибкой может считаться переход через определённый адрес, можно и на это флаг сделать, т.е. переход с 0177777 в 0 или, как у вас, с 0157777 на 0160000. p.s. например, у меня в "гайке" контроллера scsi для двк, бит 15 взводится либо по ошибке шины, либо при возникновении резета со стороны scsi-шины, а ситуацию поясняют два других бита. Один указывает на попадание в несуществующий адрес, а другой взводится сигналом RST на шине scsi и основременно транслирует его текущее значение. Если мы успели отреагировать на возникновение сброса от какого-то устройства и сигнал всё ещё не снят, мы вычищаем очередь запросов драйвера, формируя по всем заданиям ошибку, т.к. устройства, reconnect от которых мы ожидали, сбросились, и выдаём запрос таймаута по таймеру, после ввода драйвера по которому проверяем, "ушёл" ли сигнал, если да - начинаем далее выполнять запросы обмена, если нет, то ещё можно подождать (но обычно это короткая транзакция). |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 18 октября 2017 23:22 Сообщение отредактировано: 19 октября 2017 1:11

Постом выше описывал поведение ВТ2 по памяти, по прошлым экспериментам. Но тогда стенд менее совершенен был, видимо, что-то упустил. Сейчас оно оно куда лучше оказалось. Сообщение исправил. Думал, пришел к заключению, что RQINT ВТ2 это требование прекратить передачу блока, исходящее от внешнего устройства, которое обнаружило, что что-то пошло не так. Другими словами, это сигнал от устройства, возникший во время передачи блока и служащий для аварийного завершения передачи блока. В логику IDE это не укладывается, поэтому оставлю незадействованной эту полезную фичу. ПДП для IDE обслуживает не устройство, а буфер. При обмене с буфером прерываний не возникает. Ошибок тоже. В смысле, никаких флагов, индикаторов и т.п. во время обмена с буфером нету. А прерывание от устройства, ошибки устройства у IDE обслуживаются по другим каналам, не связанным с ПДП. Пока как-то так. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Сомнения, разброд и шатание. Вот я думаю, а не слишком ли расточительно под 512ВИ1 64 ячейки пространства УВВ отводить? Как такой барский жест сочетается с умеренным расходованием ресурсов в идеологии DEC? Подкупает то, что интерфейс 512ВИ1 хорошо стыкуется с SYNC, DIN, DOUT. А противится всему этому то, что 8 плюс 2 ячейки для IDE я тоже считаю перебором. Сколько вообще ячеек позволительно контроллеру НЖМД иметь, чтоб по совести было, и никто на него косо не смотрел и не завидовал? |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

Mixa написал: 2 ячейки для IDE я тоже считаю переборомДля ДВК без специализированных контроллеров типовым следует считать адреса Самарского IDE + 100 ( 8 ) : 177720....177757 с словной выборкой. ПЗУ Самары не сложно пропатчить для новых адресов. В оригинале на адресах Самарского IDE сидят регистры 1801ВМ3. Драйвер использовать от БК11М BY.SYS, начальная загрузка - 160000G. Приводы 0 и 1 - флоп. Большие номера - винт. ТО Самарского IDE : http://zx-pk.ru/threads/26264-...-nemu.html Специфический софт для работы с IDE, очевидно, надо адаптировать под RT-11 ( т.е. косметический патч ). |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

ИМХО - 512ВИ1 надо нацепить на МПИ, как это сделано в Э-85. Ну и софт тоже от туда взять. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 20 октября 2017 1:03 Сообщение отредактировано: 20 октября 2017 1:27

Mixa написал: Сколько вообще ячеек позволительно контроллеру НЖМД иметь, чтоб по совести было, и никто на него косо не смотрел и не завидовал?Сколько надо, столько и задействуйте, сейчас конкуренции на рынке нет и никто 100500 контроллеров разных устройств не поставит в одну машину. У меня в контроллере PATA IDE 10 слов используются для доступа к регистрам диска, 1 слово для доступа к наплатному микроконтроллеру и часам, 31 слово - на пзу загрузчика, зато просто и прозрачно. А в контроллере scsi имеется 37 регистров, но доступ к ним организован по указателю на регистровый файл, в результате контроллер более правильный и занимает всего 4 слова в адресном пространстве. Думаю, 512ВИ1 следует тоже по принципу ПЦшки подключить, задействовав регистр-указатель адреса и регистр данных. p.s. я это к тому, что 4к слов на ввод-вывод у pdp-11 не позволяет быть столь расточительным, как в х86, где 64кб на ввод-вывод отведено, но и на ПиСи экономят по возможности на количестве адресов в/в. p.p.s а вот контроллер ethernetа под МПИ вовсе 2 слова занимает, хотя использует здоровенные структуры в памяти. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

MM написал: ИМХО - 512ВИ1 надо нацепить на МПИ, как это сделано в Э-85. Ну и софт тоже от туда взять.К воронежцам у меня двойственное отношение. Специализация на копирвании атрофировала конструкторскую мысль, поэтому отношение настороженное. И уж точно нельзя делать "как это сделано в ...". Именно по причине убивания конструкторского навыка. |

| andyTh |

NEW! Сообщение отправлено: 20 октября 2017 15:14

К воронежцам или к дековцам?    |

| Сейчас на форуме |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Mixa написал: И уж точно нельзя делать "как это сделано в ...". Именно по причине убивания конструкторского навыка.Так у них задание было dec pro325/pro350 скопировать, там не до творчества было. А если желаете сделать часы, которых ни у кого нет на таких машинах - сделайте контроллер i2c, на него и часы, и пзу, и nvram, и датчики всякие можно будет посадить. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Mixa написал: К воронежцам или к дековцам?К воронежцам. Настороженное. Заочное. Вот лежит в коробочке 1807ВМ1, вроде симпатичный зверек, но что-то останавливает. Это что-то — иррациональное. Собственно, как и все, что здесь на форуме. Кроме продаж. Кстати, справедливости ради, конкретно в 1807ВМ1 дополнительно останавливает и идея, идущая от дека, именно - программирование режима работы при начальном старте. И 1804 как по маслу воспринимался только при чтении Мик-Брик. Запоем и не оторваться. И 531 серия печка и жрет. Хотя как имеющая в своем составе ГГ1 или как ЛН1/ЛА3 для генератора на 32 МГц - полезна. Anonymous написал: сделайте контроллер i2cПеравя реакция — не, максимум, что позволительно это 1556Х[Л,П] и 556РТ1. Вторая мысль - он же прост, сдвиговый регистр и обвязка. Посмотрел, когда он был придуман, - в начале 80-х, годится. Надо подумать, мысль интересная. |

| andyTh |

NEW! Сообщение отправлено: 20 октября 2017 17:11

Mixa написал: К воронежцам. Настороженное. Заочное. Вот лежит в коробочке 1807ВМ1,Первый пункт означает настороженное отношение именно к дековцам. Ибо воронеж порой вплоть до расположения компонентов на плате и дорожек... 1807ВМ1 тоже как бы не без аналога мягко говоря  |

| Сейчас на форуме |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Это все так. Но от дека у меня есть AlphaStation 255, и я ее берегу как экспонат. Alpha - событие знаковое. 1804, хоть она и из Воронежа, у меня проходит по категории AMD. Электронику-60 экспонатом не хочу. Она большая, глючная, и вентиляторами дребезжит, такой характерный рокочуще-звенящий звук, ну знаете, его невозможно не знать. А вокруг дека легенда, аура и восторги. Я не фанат, восторга поиметь не случилось, но к легенде прикоснуться и любопытно, и хочется. Через ангстрем и интеграл с транзистором прикасаться, как по мне, вполне годится. Не глючит и не дребезжит. Не, мож я конечно не с той стороны к деку захожу, но что уж есть, то есть. |

| andyTh |

NEW! Сообщение отправлено: 20 октября 2017 19:53

Была у нас в городе фирма комповая. На заре так сказать  И вот на выставке толи в 93, то ли в 94 году на стенде этой фирмы я увидел материнку. С 4 рогатыми альфами. И кучей памяти. Тусил возле неё долго. Впечатления остались и по сей день. Через несколько лет под рукой некоторым образом оказался класс с Э85, ещё чуть позже с ещё одним не в своём уме поднимали СМ4. Но ни Э85, ни СМка не оставили того неизгладимого впечатления, как тот монстрик. Хотя нет, звук вентилятора от 9005 помню  . .В следующий раз дековские железки попались на глаза несколько лет назад. Вот, затянуло. Перевидел я в принципе не так и мало, но впечатлений, сравнимых с восторгом от той материнки пожалуй я смог бы пересчитать. |

| Сейчас на форуме |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 22 октября 2017 20:53 Сообщение отредактировано: 22 октября 2017 20:55

В общем, с 512ВИ1 решил пока повременить. Было бы, конечно, логично поместить ее на шину с прямыми АД, которая необходима для 588-й серии и из-за этого как бы уже есть и типа бесплатно. Но она концептуально чужая на плате IDE, хоть и тоже из Минска. Земляки земляками, а дело делом. К тому же, плата маленькая. И еще, сейчас связующая логика достаточно внятна по своей структуре и хорошо впихивается в ХП4. ВИ1 вносит навороченность, которую хочется избежать. Так что, RTC окладываются, но не исключаются. Шесть линий CS селектора УВВ 588ВТ1 используются для выбора: IDE CS0 IDE CS1 КПДП 588ВТ2 Регистр RA контроллера прерываний 588ВН1 Регистр RB контроллера прерываний 588ВН1 Регистр RS контроллера прерываний 588ВН1 При этом занято 16 ячеек пространства УВВ, 8 для IDE CS0, 2 для IDE CS1, 3 для 588ВТ2 и по одной на каждый регистр 588ВН1. Ровно 16. И это единый блок, при адресации меняются только АД4..АД1. Вот такое хитрое преобразование адресов будет, чтоб 588ВТ1 активировала нужный CS. Не при деле останутся два CS от селектора УВВ 588ВТ1, но все равно ВИ1 в эту компанию просто так не вписывается, логика преобразователя вылезает за пределы ХП4, а дополнительных корпусов иметь не хочется. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

А зачем вообще 588ВТ1 нужна там? Да ещё этот бесполезный и тормозной монстр не в нативном режиме, раз у неё разные CS разный диапазон охватывают. Если ХП/ХЛ используете, на них куда компактнее и проще же... |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Ну да, из кубиков с буквами П, О, А, Ж сложить слово Счастье, примерно так. Ставим призмы, зеркала и т.п., смотрим в дырочку, читаем: "Счастье", и на этом успокаиваемся и радуемся. |

| andyTh |

NEW! Сообщение отправлено: 24 октября 2017 9:40

Вы коллегу Анонимуса то послушайте... Он имеет большую практику в складывании из этих и не только этих кубиков  |

| Сейчас на форуме |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Дык слушаю, со всем уважением, еще, помнится, в mo.dec на мои глупые вопросы отвечал  Концепция немного меняется. От ВТ1 пока не отказываюсь, ее тормознутость сочетается с общей тормознутостью проекта. Попробую порисовать, чтобы получилось следующее: Блок УВВ платы IDE с ее DMA и прерываниями занимает 8 ячеек. Они декодируются непосредственно в 8 линий CS ВТ1. Три линии группируются по ИЛИ: CS0,1,2 -> CS КПДП CS3 -> CS регистра режима контр. прерываний. Регистры векторов не используются, код вектора задается "механически" на ногах ВН1. Можно переключателями. CS4 -> IDE_CS0 CS5 -> IDE_CS1 CS6 -> индекс-счетчик адреса регистра для IDE_CS0/1, с возможностью автоинкремента CS7 -> пустой что ли? Надо подумать, подо что заюзать. Можно под один регистр вектора ВН1, для большей гибкости (а нужна ли она??). Можно под еще че-нть полезное. Упрощения: убираем хитрое преобразование адресов, убираем необходимость подстановки адреса 0 для IDE в режиме DMA Усложнения: пока не оценивал, буду рисовать Бонусы: автоинкремент индекса регистра IDE_CS0 позволяет передавать адресный блок харда и следом команду тоже по ПДП. Удобно же, разложил адрес сектора, написал команду, зарядил ПДП и сказал фас. И дальше оно все само. |

| bigral

Junior Member

Всего сообщений: 133 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 6 мая 2012 |

вопрос на засыпку и ГЛАВНЫЙ, схемы будут того что заработало уже? |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 25 октября 2017 12:02 Сообщение отредактировано: 25 октября 2017 12:22

Работает не схема, работает концепция. Схема это одно из многих возможных отражений концепции. В этой схеме есть спорные фрагменты, образовавшиеся в результате компромиссов, и в общем случае такое не подлежит тиражированию. Поэтому если схему и выкладывать на всеобщее обозрение, то это в некотором смысле ответственность, и нужно подробным образом, на уровне учебника, разжевывать, почему так делать не рекомендуется. А такое обязательство брать на себя не хочется. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Хотя, почему бы и не показать. А сомнительные места лучше не повторять. Одно из них - выход триггера-защелки DD8 КП2 с сигналом BS уходит прямиком на внешний разъем, без буфера. Принудительное изменение уровня сигнала на этой линии перекидывает триггер. Это плата с микропроцессором, от нее идут сигналы к памяти и буферам, там дальше все регулярно и очевидно.  |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Разрисовал связующую логику для платы IDE с ПДП, между буферизированной шиной МПИ, микросхемами 588 серии и шиной IDE. В соответствии с текущим пониманием тонкостей работы используемых экземпляров 588-й серии. Структура этой логики заметно отличается от того, к чему привык, разрисовывая подобное для 580, 1810, Z80. А привык к тому, что обычно получается экономно и в некотором смысле эффектно. Сейчас об эффектности речи нет, лишь бы уместилось компактно. В общем, результат где-то на троечку, но по-другому и не получается. Симпатичная программная модель не всегда означает, что электрическая реализация тоже на высоте. Все-таки, шина МПИ на выводах микросхем это проблема, если вдруг возникает необходимость в буферизаци или еще какой коррекции. Из микросхем нужно было выводить заготовку шины и сигналы управления шинными буферами. Чтоб и между собой на плате стыковалось, и чтоб межплатной шиной управлять. Но, имеем то, что есть, без вариантов. Вот что получается по предварительной прикидке: - Самая нерегулярная часть связующей логики помещена в одну ХЛ4. Но нерегулярны только четыре сигнала, остальные 4 выхода это очень простые функции от входов, типа 2И или даже просто НЕ. Ресурс израсходован неэффективно, нерегулярность и та простая, ну и хрен с этим, зато один корпус. - ЛИ1 для формирования 4 сигналов как функция ИЛИ в отрицательной логике. - ЛЛ1 для формирования 2 сигналов как ф-ция И в отрицательной логике, и два повторителя. - 561ТВ1, формирование запросов на ПДП по протоколу чередования циклов ПДП и ЦП, и генерация таймаута шины в цикле ПДП. - ИЕ7 индексный регистр-счетчик для адресации IDE. - две RC-цепочки для формирования задержек. - три диода, ф-ция ИЛИ в отрицательной логике, усиленная повторителем на четвертинке ЛЛ1. Почему не 3И ? Да потому что и так все вразнос пошло, раз уж RC-цепи появились, не-ТТЛ серия, то и это можно. Гулять так гулять. У ИЕ7 +1 считает задники обращений по IDE CS0. На -1 заведен старший разряд, запрещая счет, если там 0. То есть, получилось: - Разряды 0-2 адрес, разряд 3 разрешение автоинкремента. - Автоинкрементируются только обращения к IDE CS0. (и в циклах ПДП тоже) - Автоинкремент автоматически запрещается после обращения по адресу 111, новый адрес при этом 000. То есть, если заполнение адресной инфы и команда на чтение делаются с автоинкрементом, то для чтения буфера данных адрес выставлять не требуется. Это удобно. Если ИЕ7 заработает так, как написано, то это будет достаточной компенсацией за шероховатость остального. И если 561ТВ1 оправдает надежды, на него возлагаемые, то это будет еще лучше. ТВ1 там запланирован, потому что не требует вообще никакой обвязки, стыкуется со всеми сигналами сам. Концепция вроде бы спасена, угроза отведена. Теперь все это нужно будет отмакетировать и подтвердить концепцию. |

| andyTh |

NEW! Сообщение отправлено: 26 октября 2017 14:09

Просто спрошу, ок?  У вас тем или иным образом вписалась в концепцию ХЛка. Может быть тогда вписалась бы и к примеру EPM7128? И по теме, а где задержки поставили? |

| Сейчас на форуме |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 26 октября 2017 17:52 Сообщение отредактировано: 26 октября 2017 18:11

andyTh написал: Может быть тогда вписалась бы и к примеру EPM7128?Это шаг к тому, чтоб все сделать резиновым и безалкогольным, внутри фпгашки. 7128 у меня вроде даже где-то валяются приготовленными, но там были идеи относительно 1806ВМ2. Может и пробьет когда на безумие. Но только после этого безумия. andyTh написал: а где задержки поставили?Одна отсчет таймаута шины в цикле ПДП, другая задержка READY в ответ на IOWR от DMA контроллера в сторону девайса, с целью уширения этого IOWR. Если READY заземлить (всегда активен), то строб IOWR коротким получается, 100 нан или менее. Не помню, проглатывает такое IDE или нет, но некомфортно, увеличиваю до 200-250. ЗЫ EPM7128, говорите? 128 триггеров? На ней одной имхо можно сваять контроллер IDE вместе с ПДП и интерфейсом МПИ с прерываниями. И еще какую-нибудь свистелку. Но туда сразу просится до кучи и интерфейс ОЗУ, ПЗУ, начальный пуск. Т.е. ВМ1, эта CPLDшка, ОЗУ, ПЗУ, IDE, еще-что-то, и все на маленькой плате. Но тогда ВМ1 выпадает из концепции, ВМ2 кмоповский более гармонирует. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 26 октября 2017 22:00 Сообщение отредактировано: 26 октября 2017 22:20

Встал перед выбором. Какой из двух лучше? Винницкий или п-посадский? "Октябрь" вроде более в тему, 100-летие на носу. Или ТВ1А лучше, чем просто ТВ1?  Ой-ёё.. В книжке у него клок спадом  , а на самом деле подъемом .. Блин, узел переделывать, а ведь ничего лишнего не осталось. Один инвертор с ОК нужен теперь, наверное, просто транзистором обойдусь. , а на самом деле подъемом .. Блин, узел переделывать, а ведь ничего лишнего не осталось. Один инвертор с ОК нужен теперь, наверное, просто транзистором обойдусь. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Mixa написал: Какой из двух лучше?Критерий истины - практика. Берем микросхему, впаиваем, берем осциллограф, смотрим. Сачала КР561ТВ1А. КПДП программируется на пересылку блока из 3 слов. SACK, SYNC, RPLY и DMA_Active. (У 588ВТ2 он называется EM, похоже на Enable Memory, но со смысловой привязкой беда, какая Memory и почему Enable). КПДП переводится в активное состояние по команде от процессора, это вызывает установку DMA_Active. Окончание пересылки блока индицируется снятием DMA_Active.  Циклы DMA не начинаются, пока не появится запрос DMA_RQ. Эти запросы и их снятие формируются синхронно с установкой SYNC, запрашиваются в цикле ЦП, снимаются в цикле ПДП. Такой алгоритм обеспечивает чередование циклов ПДП и процессора. Формируются они как раз этим самым ТВ1.  На первый взгляд все хорошо, но если посмотреть на окончание ПДП с увеличением, то будет видно вот что. Это снятие DMA_Active:  А это снятие DMA_RQ. Оно задержано относительно синхронизирующего спада SYNC почти на 300 нс и находится в опасной близости от снятия DMA_Active. Опасной потому, что если еще немного повременить со снятием DMA_RQ, то это будет воспринято как запрос на пересылку следующего блока. DMA_Active при этом останется активным и начнется пересылка блока длиной 65536 слов. Заряд такой мощности способен дважды уничтожить весь мир и прощай Hello, world!  Играть со спичками рядом с ядерным детонатором не хочется, поэтому пришлось раздобыть КР1561ТВ1. И сразу обозначилась разрядка международной напряженности, задержка уменьшилась раза в три и отошла от опасной черты:  К тому же наклон фронтов ТВ1 перестал контрастировать с сигналами от ВМ1, поэтому правильный ответ - КР1561ТВ1. Ставим галочку. Хотя, казалось бы, при взгляде с высоты птичьего полета, картина как бы и не поменялась:  Семафор открыт, продолжение будет. |

| MM

Advanced Member

Откуда: Павловский Посад Мск.обл. Всего сообщений: 3418 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 2 авг. 2013 |

Mixa написал: 1561Лучше этого тихохода оставить в покое. Выбор профессионала - 1564  |

| andyTh |

NEW! Сообщение отправлено: 28 октября 2017 15:37

Mixa написал: Ой-ёё.. В книжке у него клок спадомВ последнее время я перестал пользоваться книжками для этого дела. С одной стороны конечно из за того, что приделали ноги двум моим Шило, а с другой держать в голове все опечатки? Гуглим "аналог" нужной микрушки и читаем даташит от первоисточника. Понятное дело, что попадаются микросхемы и без аналога (исчезающе редко) или с корёженной цоколёвкой, но как бы в 99.9% способ работает. |

| Сейчас на форуме |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

MM написал: 15641564 я бы с удовольствием, только мне позарез ресет нужен в положительной логике. andyTh написал: приделали ногиВ Шило, кстати, все правильно. Но у меня очень давно бумажный Шило тоже куда-то пропал, я даже и не помню, какой именно из Шил. Я этот с полки взял и посмотрел в нем: (сорри за полосы, освещение люминесцентная лампа)   |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Блин, засада ... Заранее не обратил внимание на SACK, решил, что это некий аналог BSY, только от другого ведущего, и заложился на то, что они не перекрываются.. А вот и нет. BSY еще не снят, а SACK уже появился. И SYNC еще активен! Перекрытие 300 нс. И кто, спрашивается, управляет шиной ??? У меня встречные буфера на SYNC, WTBT, DIN, DOUT. В одном направлении включается при помощи BSY, в другом при помощи SACK. В результате 300 нс какого-то идиотизма на шине, с конфликтами уровней и прочей "прелестью". Ушел думать. |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 1 ноября 2017 1:12 Сообщение отредактировано: 1 ноября 2017 1:15

Mixa написал: Заранее не обратил внимание на SACK, решил, что это некий аналог BSY, только от другого ведущего, и заложился на то, что они не перекрываются.. А вот и нет. BSY еще не снят, а SACK уже появился. И SYNC еще активен! Перекрытие 300 нс. И кто, спрашивается, управляет шиной ???В стандарте Q-Bus описана следующая последовательность запроса ДМА. 1. Устройство начинает запрос ДМА выставлением DMR. 2. Процессор подтверждает запрос ДМА выставлением DMG ( сразу после выставления DMR / снятия SACK, смотря что позже ). 3. Устройство, приняв DMG, активирует режим ДМА выставив SACK ( сразу после снятия SYNC / снятия RPLY, смотря что позже ) и сняв DMR. 4. Процессор снимает подтверждение DMG сразу после выставления SACK устройством. 5. Процессор также снимает DMG в случае снятия устройством DMR до выставления SACK или отсутствия SACK в течение 10 мкс после выставления DMR. 6. После снятия DMG при активном SACK процессор останавливается до снятия SACK устройством. 7. При рефреше памяти через шину - устройство не должно выполнять больше 4 циклов DATI / DATO или 2 циклов DATIO за один раунд ДМА. 8. После снятия устройством SACK - процессор ожидает снятия устройствами SYNC и RPLY, после чего возвращается к работе с шиной. 9. Устройства должны снять с шины сигналы DATA, BS7 и WTBT не позже, чем через 100 нс после снятия SYNC. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 1 ноября 2017 13:17 Сообщение отредактировано: 1 ноября 2017 13:19

_Patron_ написал: 3. Устройство, приняв DMG, активирует режим ДМА выставив SACK ( сразу после снятия SYNC / снятия RPLY, смотря что позже ) и сняв DMR.У 588ВТ2 есть сигнал, по смыслу похожий на SACK. Он везде называется по-разному, минскую терминологию специально приводить не буду, она какая-то странноватая. Поэтому пусть будет SACK. Но на самом деле это не чистый SACK, потому что вышеприведенный п. 3 не выполняется, этот сигнал ставится сразу по приходу DMG без ожидания снятия SYNC. Я его использовал как SACK и ничего хорошего из этого не получилось. Хорошо, пусть это будет Early SACK, ESACK его назовем. Patron, спасибо большое за разъяснения, у меня какая-никакая а шина, поэтому буду подгонять обмен сигналами в направлении этого протокола. А то уж всякие совсем грязные хаки в голову полезли, и от этого стало грустно. Дальше становится интереснее. Как определить момент для выставления настоящего SACK? Отслеживать шинные SYNC и RPLY внешними схемами не хочется, нафига тогда эта большая ИС ВТ2, большая - подразумевается умная, а как иначе? Посмотрел повнмательнее на поведение ВТ2. Она все-таки следит за шиной, дожидается окончания SYNC и только после этого начинает свой цикл. Начинает она его с формирования интервала времени при помощи внешней RC цепочки. И если бы не эта внешняя хрень, узнать, когда эта БИСина задумывает сделать свой цикл, невозможно в принципе. Только угадывать внешними схемами, но это ж фу-у-у.. Единственная зацепка, единственный шанс для ВТ2 остаться контроллером ПДП в этом изделии. Значит, так тому и быть, будем формировать цифровой сигнал из аналогового. Процесс - быстрый разряд C через открытый ключ до нуля и закрывание ключа с последующим медленным зарядом через R до напряжения питания, соответственно, сигнал это короткий отрицательный импульс вниз от питания и обратно. Напрашивается следующее решение. RS триггер, ESACK в своем пассивном состоянии держит его в одном положении. ESACK активируется, отпускает удержание триггера, а импульс на C перекидывает триггер. В конце цикла пассивный ESACK перекидывает его обратно. Как раз правильный SACK на этом триггере и сформируется. Пошел думать дальше, из чего этот триггер сделать  Я как-то где-то делал несимметричный RS триггер (внутри ХЛ8 емнип, одна макроячейка всего), логически - закольцованные И и ИЛИ, оба без инверсии. Оба выхода прямые (или оба инверсные). Второй вход И это /R, второй вход ИЛИ это S (если считать, что выходы прямые). Как раз своей разнополярностью R и S для этого триггера SACK подходят. Но для превращения в шинный SACK его нужно пропустить через повторитель с ОК. В любом случае ресурсы нужно изыскивать. Ну что, не все уж так и плохо, только неожиданными фишечками схемка обрастает. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

SACK триггером RS укоротил. Получилось как было задумано, SACK и BSY не перекрываются, буфера не конфликтуют, сигналы как конфетки. Теперь озадачен другим. Квитирование все равно не стало таким, как по протоколу Q-bus. Сейчас так: 1. Устройство выставляет DMR 2. Процессор отвечает DMG, устройство тут же снимает DMR, ЦП следом снимает DMG. 3. Устройство ждет снятия SYNC, после снятия выставляет SACK. 4. Устройство выполняет цикл ПДП, снимает SACK 5. Управление шиной возвращается ЦП. Смущает наличие промежутка времени, хотя и короткого, но во время которого все квитирующие сигналы пассивны, шина как бы ничья. Между концом SYNC и началом SACK она ничья. Реально она может быть ничьейй только в отсутствии памяти состояний у процессора. Есть подозрение, что это не так, нужно будет проверить, не подавать SACK и посмотреть, начнет процессор свой новый цикл или нет. Также проверил вариант с SACK не задержанным, но с задержанным управлением буферами. Все отлично работает, но наложение SACK на еще активный цикл шины ЦП протоколу не соответствует. С окончательным вариантом реализации определюсь после того, как станет понятно, отпускает или нет процессор шину после квитанции DMR - DMG - /DMR - /DMG и без SACK, если да, то сделаю задержанный SACK, если нет, то оставлю SACK в исполнении ВТ2, а задержу только управление буферами. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 9 ноября 2017 12:33 Сообщение отредактировано: 9 ноября 2017 12:51

Как оказалось, квитанции DMR - DMG это не более, чем обмен любезностями. Если SACK после этого обмена не подать, процессор продолжит свои циклы, как обычно. Стало быть, делаем по плану Б, то есть налезаем ранним SACK на хвост цикла ЦП. С другой стороны, ЦП сам напрашивается налезть ему на хвост, просигналив DMG. DMR: дай поиграть DMG: бери /DMR, SACK: беру /DMG: отдашь, как наиграешься (активный SACK не мешает закончить текущий цикл, но препятствует началу нового цикла ЦП) /SYNC: вижу, ты свое закончил, переключаю буфера. /SACK: отдаю, надоело Если делать более приближенно к протоколу: DMR: дай поиграть DMG: бери /DMR: понял /DMG: ну да (непонятная пауза, нужно спешить выставить SACK, пока не началось... SYNC закончился, ставим SACK!) SACK: ну этта, я типа взял, ага? (нет ответа) /SACK: отдаю, надоело Первый вариант выглядит более осмысленным. Так и делаем. В узле индекс-регистра-счетчика ИЕ7 поменял на ИЕ13. Не углядел, что у ИЕ7 вход -1 может работать как запрет счета только для триггера младшего разряда. С ИЕ13 все правильно получается, с той разницей, что автоинкремент разрешен нулем. Индекс загружается значением адреса и битом запрета инкремента адреса, т.е., чтоб поработать только с регистром 3, к примеру, нужно загрузить ^B1011, а не 3. Ну или 100003, смотря куда этот бит прикрутить. Слегка противоестественно, но машине пофиг. А если вдруг свободный инвертор нарисуется после всего, то в этом узле его можно будет утилизировать в первую очередь. |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 9 ноября 2017 18:04 Сообщение отредактировано: 9 ноября 2017 18:20 |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 9 ноября 2017 18:18 Сообщение отредактировано: 9 ноября 2017 18:31

Mixa написал: непонятная пауза, нужно спешить выставить SACK, пока не началось...Пауза гостированная = 10 мкс ( 64 такта ). В момент выставления DMG запускается счётчик на 64 такта, который тикает параллельно с ожиданием RPLY и снятием SYNC. Процессор гарантированно снимает SYNC до обнуления счётчика. Процессор не начинает новый цикл шины при активном сигнале DMR до истечения таймаута SACK. В момент обнуления счётчика ожидание SACK прекращается и процессор возвращается к нормальной работе. Не факт, что у ВМ1 это так, но это так по стандарту Q-Bus. Таймаут SACK не может быть меньше таймаута RPLY именно для того, чтобы даже после снятия SYNC по таймауту RPLY - всё равно оставалось время для ожидания выставления SACK. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Вечером попозже осциллограммы приложу, с ними нагляднее. У меня процессор до ожидания SACK не доходит (вопрос, есть ли такое состояние у ВМ1, ожидание SACK?), еще до окончания SYNC ВМ1 выдает DMG, на что сразу снимается DMR и следом в ответ DMG тоже. SYNC еще активен. 588ВТ2 такую реакцию на DMG предлагает, приходится приспосабливаться простыми средствами. |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 9 ноября 2017 18:45 Сообщение отредактировано: 9 ноября 2017 18:56

Mixa написал: еще до окончания SYNC ВМ1 выдает DMG, на что сразу снимается DMR и следом в ответ DMG тоже. SYNC еще активен.Процессор действует по стандарту - приняв DMR выдаёт DMG и запускает таймер ожидания SACK. По стандарту, в случае снятия DMR до прихода SACK - ожидание SACK прекращается немедленно. Если устройство выдаёт SACK после снятия DMR - это нонсенс. Устройство должно выдавать SACK до снятия DMR и DMG. Пока не снят DMR - активен DMG. Пока активен DMG - тикает таймер ожидания SACK и процессор не может начать новый цикл шины. Когда таймаут SACK истекает - процессор снимает DMG, что означает игнор DMR, отказ от ожидания SACK и продолжение обычной работы. Решение проблемы ( на мой взгляд ) - защёлкивание "нашего" DMR до выставления "нашего" SACK. Тогда всё будет по стандарту и процессор не снимет DMG до истечения таймаута SACK. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

_Patron_ написал: Если устройство выдаёт SACK после снятия DMR - это нонсенс. Устройство должно выдавать SACK до снятия DMR и DMG.У меня ВТ2 выдает SACK одновременно со снятием DMR и до снятия DMG. Понятно, почему я не увидел состояние ожидания SACK. А процессор такой поспешности не удивляется и не сопротивляется, есть мысль на этом и остановиться. _Patron_ написал: Решение проблемы ( на мой взгляд ) - защёлкивание "нашего" DMR до выставления "нашего" SACK. Тогда всё будет по стандарту и процессор не снимет DMG до истечения таймаута SACK.Вроде как да, и реализуемо, и картинка по стандарту выходит. Но ВТ2 ничего не знает про то, что его SACK задержали и нужно соблюсти политес в виде подождать конца SYNC, выставить свой SACK и уж потом выставлять свой SYNC. Он свой SYNC выставляет по факту снятия SYNC от ЦП, немного подождав. Не, не буду красивую картинку протокола рисовать, другим bus masters, если такие вообще появятся, это не помешает. |

| _Patron_

Member

Откуда: Москва Всего сообщений: 146 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 19 дек. 2012 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 9 ноября 2017 20:08 Сообщение отредактировано: 9 ноября 2017 20:22

Mixa написал: другим bus masters, если такие вообще появятся, это не помешаетАбитражу DMA вообще ничто не может помешать, потому что в Q-Bus нет линии DMG. Вместо этого у каждого устройства есть вход DMGI и выход DMGO ( у процессора - только DMGO ). DMGO процессора поступает на DMGI первого басмастера, DMGO первого басмастера поступает на DMGI второго басмастера и т.д. Как только басмастер выставляет DMR - он отключает DMGI от DMGO, поэтому младшие басмастеры не имеют шансов увидеть DMG до тех пор, пока старшие не закончат работу с шиной. DMR - это линия, поэтому если два устройства выставили DMR - снятие DMR старшим басмастером никто не заметит, но это и не играет роли - если в момент снятия SACK активен сигнал DMR - процессор снова выставляет DMG и на этот раз его принимает второй басмастер, ожидавший своей очереди. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 9 ноября 2017 22:05 Сообщение отредактировано: 10 ноября 2017 21:50

Во,  Здесь те же, последний - переключение буфера сигналов управления. Если его использовать как SACK, а сначала я так и хотел, то остальная картина не меняется совершенно, только было подозрение, что такой SACK это нехорошо, и спасибо Patron , тоже подтвердили, что это нонсенс. Правильное слово, нонсенс. Вне концепции, стало быть.  Все работает без нареканий и сбоев, так и оставлю ранний SACK  P.S. DMG, SACK, BSY и упр. буфером. Буфер двунаправленный, одно направление открывается по BSY, другое по этому сигналу. Видно, что все хорошо, управление не перекрывается, конфликтов нет.  |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 11 ноября 2017 0:51 Сообщение отредактировано: 11 ноября 2017 0:52

Так, с ПДП разобрались, утвердили, продолжаем. Смотрю, что получилось с прерываниями. 588ВН1 имеет два входа прерываний, A и B. Задумка такая, что на INT A приходит irq14 от IDE, на INT B идет прерывание от 588ВТ2, знаменующее окончание сеанса ПДП. 588ВН1 может выдавать вектор, запрограммированный на 6-ти специально отведенных для этого входных линиях, либо из содержимого двух внутренних 7-разрядных регистров, по регистру на каждый источник прерывания. В общем, 588-я серия продолжает преподносить сюрпризы и непонятки. В данном случае трудно понять, чем руководствовались минские разработчики, выделив 6 разрядов под внешнее кодирование вектора и 7 разрядов под внутренне-регистровое, и то, как их распределили по шине АД. Если шину АД подсоединять как по справочнику (всего 7 линий, АД7..АД1, АД0 не существует, но это понятно и очевидно, что он не требуется), то гранулярность кодирования вектора как при внешнем способе, так и при внутреннем, составляет 1 слово. На практике это не нужно, обычно гранулярность 2 слова, для адреса обработчика по четному адресу слова и PSW по нечетному адресу слова. Ради любопытства попробовал закодировать вектор по нечетному адресу слова, и расположив в памяти адрес входа в процедуру и PSW "с перекосом" соответственно, увидел, что так тоже работает. Но так никогда не делается, зачем такая возможность - совершенно непонятно. 7 разрядов регистров покрывают область векторов 000..376 полностью, внешние 6 разрядов только половину (старший разряд устанавливается в 1), то есть покрывается вторая половина области векторов. Логичнее было бы использовать в обоих способах 6 разрядов, с гранулярностью 2 слова, с полным покрытием и при это ничего лишнего. В общем, в построении концепции кирпичики оказались крупноваты и по форме несуразны, неоформившаяся идея казалась симпатичнее, но вперед движемся, от проекта не отказываемся. Пока в раздумьях, на каком из вариантов остановиться: 1. Подключение АД "по справочнику" плюсы - как бы и нету, какие могут быть плюсы в подключении, рекомендуемом справочником. Типа эталон. минусы - а вот минусы быть могут, описаны выше 2. Подключение АД со смещением на 1 разряд плюсы - гранулярность векторов 2 слова - полное покрытие векторов в режиме внешнего кодирования минусы - не могу определится, минусы это или нет. Есть особенности: сдвинутые биты регистра управления и состояния относительно "справочного" положения, неиспользуемый разряд при кодировании регистрами (выдается вхолостую на АД8), присутствие на шине не только в пределах младшего байта, выдача "1" в разряде АД8 в цикле "чтение вектора" при внешнем кодировании. Вот написал, и, похоже, что с выбором определился. Подключение со смещением на 1 разряд. Ни одна из особенностей минусом не является. Кодирование вектора внешнее, разделение источников INT A и INT B при помощи специального схемотехнического приема. У микросхемы есть вывод, на котором появляется сигнал при подтверждении прерывания INT B , если его завести на одну из линий внешнего кодирования, то на прерывания A и B будут выдаваться разные векторы. Такой трюк работает, проверил. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Mixa написал: Вот написал, и, похоже, что с выбором определился. Подключение со смещением на 1 разряд.Именно так всегда и делалось, справочники - как газеты, их после еды читать лучше. DEC же поправился, что область плавающих пользовательских векторов до 01000 простирается, а до 0400 размещаются системные вектора, т.к. системный стек расположен в верхней половине первых 64кб, а пользовательский стек находится в отображении памяти пользователя. Но это для процессоров с ДП. Mixa написал: сигнал при подтверждении прерывания INT B , если его завести на одну из линийОбычно он заводился на AD2, давая вектор-B на 4 больше вектора-A, как в большинстве устройств с несколькими векторами принято. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Anonymous написал: Mixa написал:Я почему-то решил, что вектор воспринимается только с линий АД7-АД1 , но оказалось, что и с линии АД8 тоже. На входах кодирования установил уровни, чтоб вектор 200 выдавался, а в результате прыгнуло на 600, потому что по АД8 единица передалась. Фигня, поменяю местами подключения к АД7 и АД8, будет всегда выдаваться 1 на АД7. Появляется ограничение на выбор вектора, ну и ладно, выберем какой-нибудь из второй половины системных.Вот написал, и, похоже, что с выбором определился. Подключение со смещением на 1 разряд.Именно так всегда и делалось, справочники - как газеты, их после еды читать лучше. DEC же поправился, что область плавающих пользовательских векторов до 01000 простирается, а до 0400 размещаются системные вектора, т.к. системный стек расположен в верхней половине первых 64кб, а пользовательский стек находится в отображении памяти пользователя. Но это для процессоров с ДП. Anonymous написал: Mixa написал:Ну да, так и делаюсигнал при подтверждении прерывания INT B , если его завести на одну из линийОбычно он заводился на AD2, давая вектор-B на 4 больше вектора-A, как в большинстве устройств с несколькими векторами принято.  Вначале опасался, что подтверждение VECB с большой задержкой будет проходить с линии кодирования на выход АД, но нет, все нормально, даже иголки практически нет, только намек на нее. Вначале опасался, что подтверждение VECB с большой задержкой будет проходить с линии кодирования на выход АД, но нет, все нормально, даже иголки практически нет, только намек на нее. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 11 ноября 2017 16:22 Сообщение отредактировано: 11 ноября 2017 20:14

Вектор прерывания это слово целиком, имеют значение все 15 разрядов. 588ВН1 у меня упрятан за двунаправленный буфер с инверсией и выдает вектор 300, по 7-ми линиям АД, АД8-АД2. Остальные линии буфера на стороне ВН1 ничем не драйвятся, находятся в состоянии высокого импеданса и там присутствует сам собой получившийся потенциал логического нуля, сохраняющийся за счет емкости шины. Ноль этот обусловлен тем, что системная шина (инверсная сторона буфера) притянута к питанию (то есть на ней лог.0 ), в цикле приема вектора ее никто не драйвит и этот лог. 0 передается на неинверсную сторону, разряжая шину со стороны ВН1. По IAKO & DIN буфер переключается, потенциал на шине сохраняется, она начинает чем-то заряжаться, но делает это очень медленно и ноль там сохраняется до конца цикла IACK. То есть, вроде как все детерминировано, но такое положение вещей мне сильно не нравится, удержание потенциала шины в критический момент ее чтения только за счет ее емкости в концепцию ну никак не входит. Я решил проверить, какие разряды ВМ1 воспринимает как вектор прерывания. Расставил ловушки по адресам 1300, 2300, 4300, 10300, 20300, 40300 и 100300. Стал по очереди притягивать линии на неинверсной стороне сопротивлением к питанию. Ловушки срабатывают все. То есть, при выдаче вектора прерывания нужно заботиться о том, чтобы передавались все биты слова без искажения. Блин, появилась забота, какими средствами это сделать. Возвращаться к подключению "по справочнику"? Тогда получится: АД7 всегда единица, вектора из второй половины таблицы. АД6-АД3 кодируются произвольно. На АД2 завернут VECB, разделяя INT A и INT B. АД1 кодируется нулем с целью удержания потенциала шины. Теперь, с учетом нового понимания, это не просто какой-то мусорный разряд, а разряд, занимающийся удержанием потенциала. Причем этот потенциал программируется  , не хухры-мухры. АД0 можно оставить условно-неопределенным, в емкостном нуле. Осталось разобраться со старшей половиной шины. А не подвести ли туда 8 диодов от линии инверсное IAKO & DIN ? Другой вариант - отключить вообще этот буфер по IAKO & DIN . Процессору потенциал сформируется подтяжками на системной шине. , не хухры-мухры. АД0 можно оставить условно-неопределенным, в емкостном нуле. Осталось разобраться со старшей половиной шины. А не подвести ли туда 8 диодов от линии инверсное IAKO & DIN ? Другой вариант - отключить вообще этот буфер по IAKO & DIN . Процессору потенциал сформируется подтяжками на системной шине.Надо подумать. P.S. Подумал. После раскидывания узлов по "колокольчикам", остался один ИЛИ-НЕ. Если на него подать /DIN и /IAKI , на выходе получится как раз /OE для "верхнего" буфера. /OE "нижнего" буфера - вечный ноль. Теперь нужно подключать живой IDE и смотреть, как и что там будет получаться. Задумано два отдельных прерывания на одно устройство, думаю, логично и оправдано. Одно прерывание по готовности устройства, это понятно, дал команду на чтение сектора, ушел по своим делам, прервали, пришел за данными. Другое прерывание по готовности пересылки ПДП. Запустил ПДП, ушел по своим делам, прервали, данными в памяти можно пользоваться (если чтение с диска). Если запись на диск, можно запустить ПДП и ждать прерывания уже от устройства, но прерывание от ПДП тоже может быть полезным для какого-нибудь промежуточного контроля. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Mixa, я у себя только буфер младшего байта открываю в цикле передачи вектора, таким образом старший байт всегда равен нулю за счёт подтяжек МПИ со стороны процессора. |

| Mixa

Member

Откуда: Москва Всего сообщений: 170 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 8 авг. 2009 |

Подключил IDE, попробовал читать-записывать сектора. Удивительно, оно работает. Даже получается фишка с автоинкрементом адреса IDE CS0, и даже можно заполнять регистры методом ПДП. Также сделал таймаут шины при обращении от контроллера ПДП, и тоже фурычит, и вполне вменяемое поведение получается. Случился таймаут, сеанс ПДП заканчивается, возникает прерывание, читаем регистр состояния ПДП - там ошибка, все четко. Вроде можно переносить с макета на схему, но есть шероховатость. Сейчас группы регистров по IDE CS0 и IDE CS1 адресуются своими отдельными линиями CS, и еще есть третья, идущая на запись в индекс-регистр-счетчик, через который адресуется IDE. Как известно, IDE CS1 представляет из себя тот еще костыль, один из множества уродцев из наследия, начало которому положило IBM PC. К тому же с очень малоиспользуемой функцией, и тратить на это чудо целую линию CS как-то не хотелось бы. И возникла идея объединить его с индекс-счетчиком, поместив счетчик в пустующий старший байт. Пусть оба костылика будут на одном CS, один досадный ATAшный и другой, прикольно-полезный. Высвободившийся CS пойдет на контроллер прерывания, там один из регистров вектора остался неадресованным. Таким образом, неадресованных ресурсов не остается. Это радует. Пошел перепаивать, и смотреть, что получится. |

| Anonymous

Advanced Member

Откуда: Москва(Россия) Всего сообщений: 2537 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 22 нояб. 2011 |

Mixa написал: CS1 представляет из себя тот еще костыль, один из множества уродцев из наследия, начало которому положило IBM PC. К тому же с очень малоиспользуемой функциейПочему малоиспользуемой? Там же не только программный сброс накопителя, там и разрешение прерываний от него. |

| Mixa

Member