| Объявление форума |

Если пользуетесь личными сообщениями и получили по электронной почте оповещение о новом письме, не отвечайте, пожалуйста, почтой. Зайдите на форум и ответьте отправителю через ЛС. |

Полигон-2 » IBM PC-совместимое. До 2000 года включительно » Память EDO вместо FPM в 486-е без поддержки EDO |

|

Память EDO вместо FPM в 486-е без поддержки EDO

Кто-нибудь задумывался?

| <<Назад Вперед>> | Страницы: 1 2 3 4 5 | Печать |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

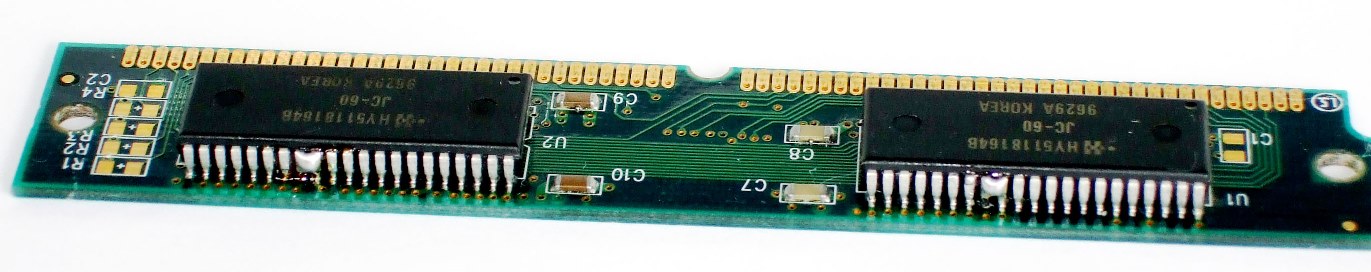

У меня совершенно дикая диспропорция имеющихся планок Simm72. EDO раз в 10 больше, чем FPM. Задался вопросом, можно ли "подружить" планки EDO с материнскими платами, без поддержки оной. Где-то читал, что EDO изначально задумывалась как полностью совместимая с FPM. Но производители то ли плат, то ли чипсетов, где-то намудрили, упростили, сделали не совсем по стандарту, и в итоге FPM работает, а EDO нет. Кстати, материнская плата socket5 Premiere PCI II "Plato" (чипсет i430NX) прекрасно работает с EDO, даже не подозревая, что это не FPM. То есть доля истины, в утверждении выше, есть. |

| AlexV2

Advanced Member

Откуда: Ростов-на-Дону Всего сообщений: 3000 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 25 мар. 2009 |

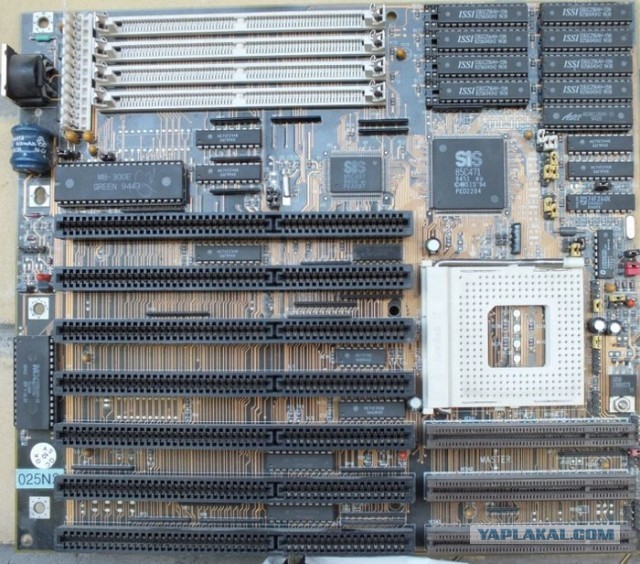

Думаю что в чипсетах дело. Например набор SIS 496/497, на одной и той же мат.плате LS-486E, в зависимости от ревизии чипсета, может работать с EDO или FPM памятью. |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Логично. Можно ли "обхитрить" систему? |

| AlexV2

Advanced Member

Откуда: Ростов-на-Дону Всего сообщений: 3000 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 25 мар. 2009 |

Rio444 написал: Логично. Можно ли "обхитрить" систему?Вот ещё что вспомнил. Есть у меня 486 мат.плата, правда она на чипсете от UMC, которая изначально работала с EDO памятью, но версия BIOS была из первых ревизий и не понимала 5X86. После обновления BIOS на более свежуою версию, процессор 5X86 стал правильно отображаться, но при этом перестала работать EDO память, плата стала на неё пищать. После отката на старую версию BIOS плата опять стала нормально работать с EDO памятью. Производитель зачем то отрубил поддержку EDO памяти через BIOS Ещё у меня полно 486-х пром.плат, которые документированно работают с EDO памятью, причем не парами а по одному модулю |

| Bobo

Advanced Member

Откуда: СПб Всего сообщений: 3628 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 16 авг. 2007 |

Rio444у меня на интеле 486м какие-то модули через раз стартовали какие-то наполовину виделись но винда когда начинает всю память тестировать вываливается в синий экран |

| AlexV2

Advanced Member

Откуда: Ростов-на-Дону Всего сообщений: 3000 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 25 мар. 2009 |

Не обязательно винда, любой тестмем под DOS сыпет ошибками. Не просто так в некоторых платах поддержка EDO отключена, не работают с ней корректно чипсеты, где то у разработчиков допущен баг |

| irond69

Advanced Member

Всего сообщений: 677 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 30 нояб. 2017 |

Rio444 написал: Где-то читал, что EDO изначально задумывалась как полностью совместимая с FPM.У них разное количество тактов обмена, EDO быстрее работает |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

irond69 написал: У них разное количество тактов обмена, EDO быстрее работаетСей факт, обильно размусоленный в середине 90-х не очень подтверждается практикой. Разница от 3% до отрицательной, т.е. в пользу FPM. Да и по тактам должно всё совпадать, если время доступа одинаковое. |

| i8088

Advanced Member

Откуда: г. Баку, Азербайджан Всего сообщений: 2132 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 30 янв. 2015 |

Там не в тактах дело, а во времени удержания данных на выходе, что может приводить к конфликту, очень хорошо описано в книгах М. Гука. И да нужен и чипсет правильный и BIOS. Некоторые чипсеты видимо недокументированно EDO переносят, а некоторые нет. |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 1 мая 2018 16:45 Сообщение отредактировано: 1 мая 2018 16:46

i8088 написал: А решения-то какие-то есть? Какую-нибудь перемычку поставить, буфер впаять? Вас, коллега, я и ждал. Знал, что не пропустите эту тему))) |

| i8088

Advanced Member

Откуда: г. Баку, Азербайджан Всего сообщений: 2132 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 30 янв. 2015 |

Rio444 написал: А решения-то какие-то есть? Какую-нибудь перемычку поставить, буфер впаять?Ну подумать можно об этом (около управляемого двунапрвленного буфера), но боюсь если и можно, решение будет некрасивым.... |

| Jccwu

Advanced Member

Злой и Нечуткий Откуда: Екатеринбург Всего сообщений: 3579 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 6 апр. 2013 |

Alex_Vac написал: Думаю что в чипсетах дело. Например набор SIS 496/497, на одной и той же мат.плате LS-486E, в зависимости от ревизии чипсета, может работать с EDO или FPM памятью.Если быть точным, то до буквы P на чипсете. После нее уже не подддерживает |

| wbcbz7

Full Member

Откуда: omsk || nsk Всего сообщений: 230 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 17 фев. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 1 мая 2018 21:26 Сообщение отредактировано: 1 мая 2018 21:43

i8088 написал: Ну подумать можно об этом (около управляемого двунапрвленного буфера), нона платах на i430FX/VX и VIA Apollo VP/VPX так и сделано, там стоит пара 32-битных буферов между шиной данных проца и памяти (в том же корпусе, что и кэш, обычно и находятся рядом). Еще где-то видел схему модификации планок памяти, в которой от земли отпаивались выводы /OE микросхем и на них подавался объединенные по AND линии RAS0..3 (или CAS, не помню) |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

74HCT245 или 74ALS245 не подойдут? |

| wbcbz7

Full Member

Откуда: omsk || nsk Всего сообщений: 230 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 17 фев. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 1 мая 2018 22:42 Сообщение отредактировано: 1 мая 2018 22:44

Rio444 написал: 74HCT245 или 74ALS245 не подойдут?лучше всего 74F245, но ALS (и HCT с небольшой натяжкой,  |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

wbcbz7 написал: и где-то их располагатьНа переходнике, видимо. |

| i8088

Advanced Member

Откуда: г. Баку, Азербайджан Всего сообщений: 2132 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 30 янв. 2015 |

Одного буфера не хватит, надо еще сообразить, как им управлять, и возможны подводные камни многочисленные wbcbz7 написал: на платах на i430FX/VX и VIA Apollo VP/VPX так и сделано, там стоит пара 32-битных буферов между шиной данных проца и памяти (в том же корпусе, что и кэш, обычно и находятся рядом).Эти TDX вообще говоря не совсем буферы и к поддержке EDO прямого отношения не имеют |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

i8088 написал: Одного буфера не хватит, надо еще сообразить, как им управлять, и возможны подводные камни многочисленныеПоэтому и создал тему. Пока видится так: - 4 буфера 74хх245 по 8 бит, - /WE на DIR, - /CAS на /OE. У ALS задержка 10нс. Т.е. планка 60нс становится 70нс, планка 70нс становится 80нс. ИМХО не критично. У HCT задержка 16нс. Что хуже, зато эти чипы стоят копейки. F или AHCT было бы идеально, но цена чипов делает затею бессмысленной. |

| alecv

Advanced Member

Откуда: Санкт-Петербург Всего сообщений: 5545 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 5 окт. 2004 |

Rio444 JFYI Вот дискуссия два года назад: http://www.phantom.sannata.ru/...6#pp335396 |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 3 мая 2018 9:41 Сообщение отредактировано: 3 мая 2018 9:42

Вот здесь подробно написано на тему почему EDO обычно не работает на четверках взято отсюда: http://forum.ixbt.com/topic.cgi?id=6:457:6#6 а там оно появилось из Paul's FAQ http://web.archive.org/web/200...q3.html#15 Более подробный ответ хотелось бы начать с того факта, что память EDO имеет от памяти fast page одно-единственное отличие. Если для последней линии ввода-вывода данных немедленно закрывались, как только начиналось задание адреса следующего бита (зарядка CAS в fast page схеме), то EDO (Extended Data Out) режим позволяет держать эти линии открытыми практически вплоть до окончания ввода нового адреса и соответственно начала вывода следующего бита. Тем самым память EDO разрешает одновременно считывать данные и задавать адрес следующих данных, что в свою очередь позволяет сократить длительность цикла доступа путем использования конвейерной схемы. |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Roman555 написал: А предложения-то какие? |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Rio444 написал: А предложения-то какие?По мнению автора FAQ болезнь не излечима (практически). Я понимаю, что он лучше меня разбирается в работе памяти. ИМХО, если бы был простой практичный путь, его бы уже нашли. А теоретический и сложный - на любителя. |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Так он же и рецепт даёт: память EDO имеет от памяти fast page одно-единственное отличие. Если для последней линии ввода-вывода данных немедленно закрывались, как только начиналось задание адреса следующего бита (зарядка CAS в fast page схеме), то EDO (Extended Data Out) режим позволяет держать эти линии открытыми практически вплоть до окончания ввода нового адреса и соответственно начала вывода следующего бита. Тем самым память EDO разрешает одновременно считывать данные и задавать адрес следующих данных, что в свою очередь позволяет сократить длительность цикла доступа путем использования конвейерной схемы.Четыре 74ALS245 (на модуль) должны решить эту проблему. |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Ну, если у вас получится это сделать в железе, то как говорится, респект и уважуха! Я пока не вникал во все тонкости работы FPM vs EDO, просто ознакомился, чтобы понять, что могут быть грабли, даже если в мануале, как например к LS486E, написано, что поддерживает EDO, хотя это зависит от ревизии моста. |

| Jccwu

Advanced Member

Злой и Нечуткий Откуда: Екатеринбург Всего сообщений: 3579 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 6 апр. 2013 |

узнал что у меня оказывается есть мамка с VLB поддерживающая EDO!!!  |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Jccwu написал: узнал что у меня оказывается есть мамка с VLB поддерживающая EDO!!!Что за модель? На чипсете UMC ? |

| Jccwu

Advanced Member

Злой и Нечуткий Откуда: Екатеринбург Всего сообщений: 3579 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 6 апр. 2013 |

Roman555 написал: На чипсете UMC ?на SIS  |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Jccwu проверьте пожалуйста. Есть большие сомнения, что Sis471 умеет EDO. |

| Jccwu

Advanced Member

Злой и Нечуткий Откуда: Екатеринбург Всего сообщений: 3579 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 6 апр. 2013 |

Rio444 написал: Jccwu проверьте пожалуйста.я ее пока не могу найти. Рыл свои старые темы, и нашел в одной что у меня есть такая мамка. Был крайне удивлен про EDO на VLB. Начал искать ее, но пока не нашел. |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 5 мая 2018 16:00 Сообщение отредактировано: 5 мая 2018 16:01

Даташит на SIS 85C471 ничего про поддержку EDO не знает. Очень сомнительно, что более старый SIS471 нормально с EDO работает, в то время как в более новом SIS 85С496 всю совместимость с EDO испортили и исправили только в последней ревизии |

| pbx |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 5 мая 2018 19:18 Сообщение отредактировано: 5 мая 2018 19:19

Roman555 написал: а там оно появилось из Paul's FAQТеперь понятно, почему EDO не дает прироста скорости на тех четверках, которые с ней работают. |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

i8088 написал: Там не в тактах дело, а во времени удержания данных на выходе, чтоРечь, видимо, шла о книге "Аппаратные средства IBM PC". Решил раскопать ее и нашел следующее: Установка EDO DRAM вместо стандартной в неприспособленные для этого системы может вызвать конфликты выходных буферов устройств, разделяющих с памятью общую шину данных. Скорее всего этот конфликт возникнет с соседним банком памяти при использовании чередования (Bank Interleaving). Для отключения выходных буферов EDO-памяти внутри страничного цикла обычно используют сигнал WE#, не вызывающий записи во время неактивной фазы CAS# (рис. 5.10, кривая а). По окончании цикла буферы отключаются лишь по снятию сигнала RAS# (рис. 5.10. кривая 6). Прикрепленный файл (EDO_DIAGRAM.png, 0 байт, скачан: 23 раза) |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 5 мая 2018 21:06 Сообщение отредактировано: 5 мая 2018 21:07

В подтверждение приведу еще один даташит (на EDO MICRON), в котором тоже указана возможность управлять закрытием буферов данных с помощью WE# Как я понял, можно отказаться от использования 4 м/сх 245, а просто по подъему CAS# активировать WE# Прикрепленный файл (micron mt4lc4m4e8 edo dram.pdf, 0 байт, скачан: 28 раз) |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Roman555 написал: Как я понял, можно отказаться от использования 4 м/сх 245, а просто по подъему CAS# активировать WE#Как это сделать "просто"? Что-то схема не складывается. |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Rio444 написал: Roman555 написал:К сожалению, у меня нет ответа на этот вопрос.Как я понял, можно отказаться от использования 4 м/сх 245, а просто по подъему CAS# активировать WE#Как это сделать "просто"? |

| ATauenis

Advanced Member

Откуда: Москва Всего сообщений: 2904 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 30 апр. 2015 |

Возможно, можно привлечь многоногую программируемую логику. |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

ATauenis написал: Возможно, можно привлечь многоногую программируемую логику.Думал об этом. Но это уже не совсем просто. |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 7 мая 2018 17:55 Сообщение отредактировано: 7 мая 2018 17:55

Придумал схемку, но оказалась сложной. Возможно, работать не будет вообще или, временами, неправильно. Если есть профессиональные схемотехники, - проверьте. Логика работы исходит из допущения, что при чтении не бывает активно одновременно 2 и более линий RAS0#-RAS4# . Это же допущение касается и CAS0#-CAS4# . Рисовал в программе oregano. Думал она сможет смоделировать, но с наскоку ничего не получилось с моделированием - нет в комплекте библиотек для 74xx Прикрепленный файл (edo_mod_schema1.png, 0 байт, скачан: 51 раз) |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 | |

| sde79 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 6 июня 2018 20:13 Сообщение отредактировано: 6 июня 2018 20:19

Roman555 написал: В подтверждение приведу еще один даташит (на EDO MICRON), в котором тоже указана возможность управлять закрытием буферов данных с помощью WE#Это костыль, из-за того, что у планок simm нет специального контакта для подачи ОЕ, приходится изощряться с использованием WE. А если задача стоИт просто переделать планку EDO в FPM-совместимую, то можно просто отпаять ноги ОЕ микросхем и подать на них соответственно CАS, и никакая логика не нужна. Ибо вся проблема в том и заключается, что чипы FPM отключают выводы данных автоматически при получении CAS, и сигнал ОЕ подавать уже не нужно. А EDO, получив CAS, продолжает замусоривать шину и ждать прихода ОЕ или WE в явном виде. |

| Roman555

Newbie

Откуда: Харьков Всего сообщений: 55 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 26 апр. 2018 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 7 июня 2018 11:43 Сообщение отредактировано: 7 июня 2018 12:09

Rio444 написал: Нужно отключить от земли /OE (29 нога) и соединить с /UCAS или /LCAS. Проще с /UCAS, потому что это соседняя, 30-я нога.Идеально! Респект. Проще решения не придумать. |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 7 июня 2018 11:55 Сообщение отредактировано: 7 июня 2018 11:56

Roman555 написал: sde79 написал:Вообще-то sde79 написал это, уже после реализации в железе (фото выше).можно просто отпаять ноги ОЕ микросхем и подать на них соответственно CАS, и никакая логика не нужна.Идеально! Респект. Проще решения не придумать.  Тема постепенно перетекла сюда. Там подробнее. |

| Jager |

Дабы новую тему не создавать. Плата BA2161 (скорее всего от Olivetti M4-4x4, хотя в мануале на эту серию данной мат. платы нет) на UM82C491/82C493, про поддержку EDO информации нет, однако 2х8мб EDO без проблем видит и memtest86+ проходит. Рядом с памятью есть 4 74LS245, если что. Стоит ли ожидать какие-нибудь проблемы из-за EDO памяти? |

| Rio444

Гость

Откуда: Ростов-на-Дону Всего сообщений: 8632 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 14 сен. 2014 |

Jager написал: Стоит ли ожидать какие-нибудь проблемы из-за EDO памяти?Нет. Либо работает, либо нет. Видимо этот чипсет поддерживает EDO. У UMC был такой. |

| wbcbz7

Full Member

Откуда: omsk || nsk Всего сообщений: 230 Рейтинг пользователя: 0 Ссылка Дата регистрации на форуме: 17 фев. 2014 |

Профиль | Сообщить модератору

NEW! Сообщение отправлено: 27 февраля 2019 19:31 Сообщение отредактировано: 27 февраля 2019 19:32

Jager написал: Рядом с памятью есть 4 74LS245, если что.вот и ответ на вопрос  если буферы развязывают шины данных проца и памяти, то EDO точно будет работать (вообще, если не вру, 491 нативно EDO не умел, а вот платы на 8496/8881 поддерживали и без буферов) если буферы развязывают шины данных проца и памяти, то EDO точно будет работать (вообще, если не вру, 491 нативно EDO не умел, а вот платы на 8496/8881 поддерживали и без буферов) |

| <<Назад Вперед>> | Страницы: 1 2 3 4 5 | Печать |

Полигон-2 » IBM PC-совместимое. До 2000 года включительно » Память EDO вместо FPM в 486-е без поддержки EDO |

|

| 1 посетитель просмотрел эту тему за последние 15 минут |

| В том числе: 1 гость, 0 скрытых пользователей |

| Последние |

|

| [Москва] LIQUID-Акция. Сливаются разъемы CF МС7004 и 7004А на AT и XT Пайка термотрубок Проммать s478 PEAK 715VL2-HT ( Full-Size SBC) Подскажите по 386 материке по джамперам. | |

| Самые активные 5 тем |

|